МИНОБРНАУКИ РОССИИ

Государственное образовательное учреждение высшего профессионального образования

«Санкт-Петербургский государственный электротехнический

университет “ЛЭТИ” имени В.И. Ульянова (Ленина)»

(СПбГЭТУ)

---

## ЦИФРОВАЯ СХЕМОТЕХНИКА

Методические указания по проведению

лабораторных занятий

### Внутренняя рабочая версия каф. ЭПУ

*Данный документ постоянно обновляется и совершенствуется по мере модернизации лабораторного практикума. Актуальную версию этого документа в формате PDF можно загрузить по следующей ссылке:*

[https://www.dropbox.com/s/bunsbibh43ao0gv/EPU\\_Cxt\\_Lab.zip?dl=0](https://www.dropbox.com/s/bunsbibh43ao0gv/EPU_Cxt_Lab.zip?dl=0)

Санкт-Петербург

2016

## ОГЛАВЛЕНИЕ

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Введение .....                                                                                      | 3  |

| 1. Ознакомление с лабораторным стеном и исследование простейших комбинаторных логических схем ..... | 4  |

| 1.1. Краткое описание лабораторной работы .....                                                     | 4  |

| 1.2. Общие сведения о лабораторном стенде и контрольно-измерительном оборудовании .....             | 4  |

| 1.2.1. Общие сведения о лабораторном стенде .....                                                   | 4  |

| 1.2.2. Рекомендации по сборке электрических схем .....                                              | 9  |

| 1.3. Основные теоретические сведения .....                                                          | 10 |

| 1.4. Задание на проведение лабораторной работы .....                                                | 16 |

| 2. Мультивибраторы на логических элементах .....                                                    | 19 |

| 2.1. Краткое описание лабораторной работы .....                                                     | 19 |

| 2.2. Основные теоретические сведения .....                                                          | 19 |

| 2.3. Задание на проведение исследований.....                                                        | 28 |

| 3. Исследование схем триггеров.....                                                                 | 32 |

| 3.1. Краткое описание лабораторной работы .....                                                     | 32 |

| 3.2. Основные теоретические сведения .....                                                          | 32 |

| 3.3. Задание на проведение исследований.....                                                        | 37 |

| 4. Устройства последовательностной логики на триггерах .....                                        | 42 |

| 4.1. Краткое описание лабораторной работы .....                                                     | 42 |

| 4.2. Основные теоретические сведения .....                                                          | 42 |

| 4.3. Задание на проведение исследований.....                                                        | 52 |

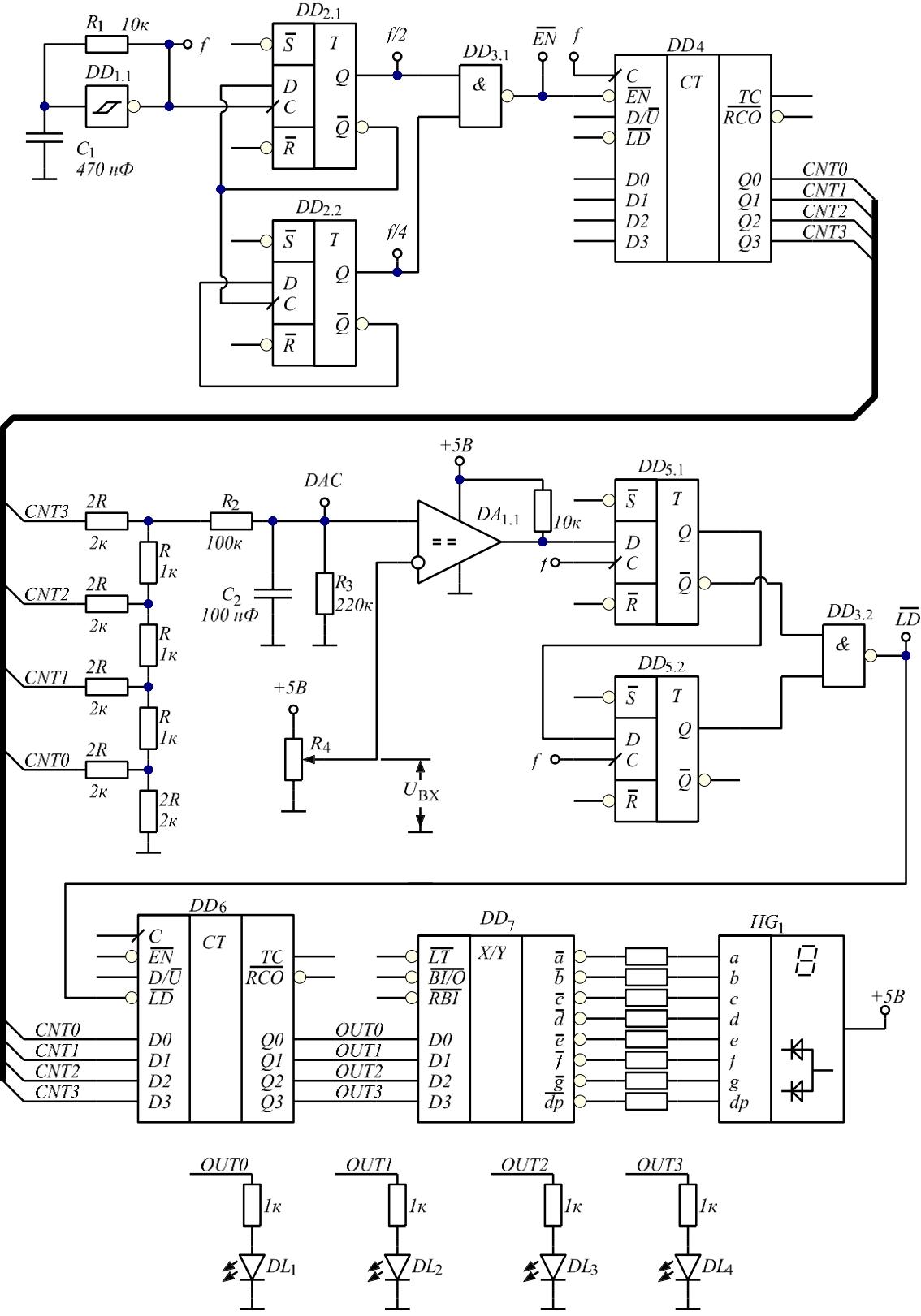

| 5. Синхронные цифровые схемы и устройства ввода-вывода.....                                         | 56 |

| 5.1. Краткое описание лабораторной работы .....                                                     | 56 |

| 5.2. Основные теоретические сведения .....                                                          | 56 |

| 5.3. Задание на проведение исследований.....                                                        | 69 |

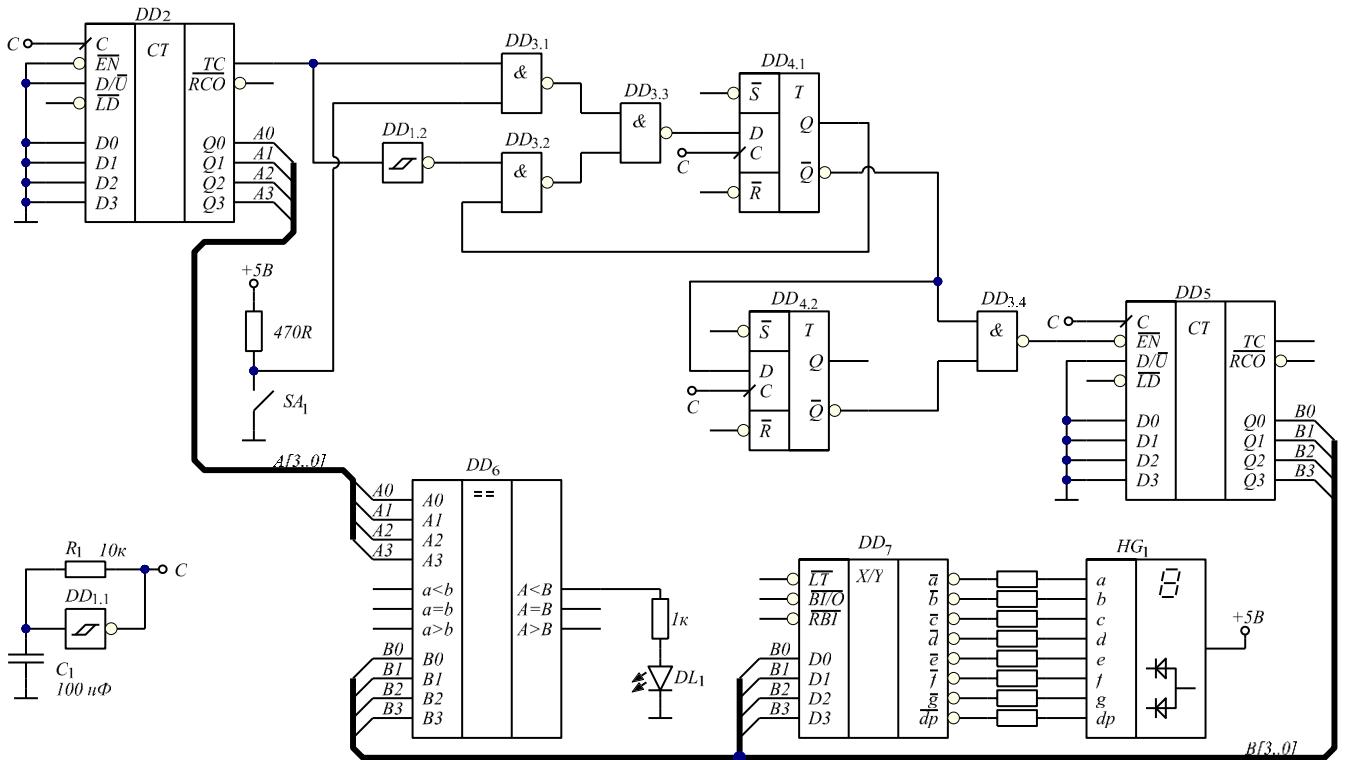

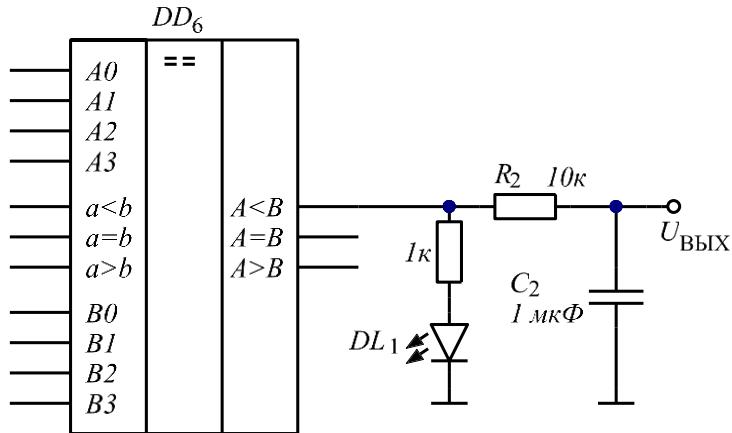

| 6. Цифровой широтно-импульсный модулятор .....                                                      | 73 |

| 6.1. Краткое описание лабораторной работы .....                                                     | 73 |

| 6.2. Основные теоретические сведения .....                                                          | 73 |

| 6.3. Задание на проведение исследований.....                                                        | 80 |

| 7. Исследование схем ЦАП и АЦП .....                                                                | 83 |

| 7.1. Краткое описание лабораторной работы .....                                                     | 83 |

| 7.2. Основные теоретические сведения .....                                                          | 83 |

| 7.3. Задание на проведение исследований.....                                                        | 90 |

## **ВВЕДЕНИЕ**

Лабораторный курс по дисциплине «Цифровая Схемотехника» является логическим продолжением работы, выполняемой студентами в рамках курса «Аналоговая Схемотехника». Подразумевается, что студент, приступающий к выполнению лабораторных работ, знаком с используемым контрольно-измерительным оборудованием, общим подходом к сборке и исследованию электрических схем, порядком выполнения лабораторной работы и протоколирования результатов наблюдений. Описанный круг вопросов достаточно подробно рассмотрен в методических указаниях к выполнению лабораторных работ по дисциплине «Аналоговая Схемотехника».

Общие требования к отчетам по лабораторным работам таковы:

1. К отчету должен быть приложен протокол выполнения лабораторной работы, подписанный преподавателем. Без протокола отчет по лабораторной работе недействителен. Перед составлением протокола в нем указывается дата, номер группы, имена студентов, выполнивших лабораторную работу, название работы.

2. Составляется один отчет на бригаду, выполнившую лабораторную работу. Бригады состоят из двух (максимум трех) человек.

3. На лабораторные работы, состоящие из двух частей, составляется один отчет, к которому прикладывается два протокола.

4. Отчет должен содержать исследованные электрические схемы и основные теоретические соотношения, описывающие их работу. Следует приводить только ключевые сведения и формулы; полностью перепечатывать методические указания и иную литературу нет необходимости.

5. Данные, полученные в результате исследований, должны быть перенесены из протокола выполнения работы в отчет, и представлены в обработанном виде: таблицы и осциллограммы следует оформлять аккуратно и читаемо.

6. Если для расчета массивов данных используется табличный процессор (например, MS Excel), в отчете должны быть приведены формулы, введенные в него для автоматического расчета значений.

7. Результаты в виде графиков и диаграмм (если есть) должны быть оформлены с соответствующим уровнем качества. В частности, оси должны быть подписаны с указанием размерности, диаграммы напряжений должны иметь заголовок, линии сетки, улучшающие читаемость. Временные диаграммы цифровых сигналов в случаях, когда исследуется только логика работы какого-либо узла, следует изображать в условных осях. В таких случаях ось абсцисс не имеет размерности, а ось ординат размечена лишь двумя метками – уровень логических «0» и «1».

8. Краткие выводы по лабораторной работе должны содержать информацию о том, соответствуют ли полученные результаты теоретическим соображениям (какие и как), при необходимости – объяснение расхождений результатов наблюдений с теорией.

**Перед тем, как приступить к выполнению лабораторных работ, при необходимости следует самостоятельно изучить лабораторное оборудование, внимательно ознакомившись с главой 1.2 методических указаний по выполнению лабораторных работ дисциплины «Аналоговая Схемотехника».**

# 1. ОЗНАКОМЛЕНИЕ С ЛАБОРАТОРНЫМ СТЕНДОМ И ИССЛЕДОВАНИЕ ПРОСТЕЙШИХ КОМБИНАТОРНЫХ ЛОГИЧЕСКИХ СХЕМ

## 1.1. Краткое описание лабораторной работы

1. В лабораторной работе изучается лабораторный стенд, содержащий цифровые микросхемы серии 7400 подсемейства НС/НСТ.

2. В качестве источников сигналов используются встроенные в лабораторный стенд переключатели.

3. В качестве индикаторов логических уровней используются дискретные светодиоды с токоограничительными резисторами.

4. При помощи кнопок и светодиодов исследуются таблицы истинности ряда логических элементов (ЛЭ).

## 1.2. Общие сведения о лабораторном стенде и контрольно-измерительном оборудовании

Краткое описание используемого лабораторного оборудования приведено в методических указаниях по дисциплине «Аналоговая схемотехника».

### 1.2.1. Общие сведения о лабораторном стенде

Стенд для сборки электрических схем был разработан на каф. ЭПУ СПбГЭТУ «ЛЭТИ» и не является серийным изделием какого-либо производителя электронных изделий. Дополнительной документации на стенд, за исключением настоящих методических указаний, не существует.

Стенд представляет собой стандартную двухстороннюю печатную плату из стеклотекстолита с установленными на ней электронными компонентами. Все интегральные схемы, содержащиеся в стенде, уже подключены к источнику питания и снабжены блокировочными конденсаторами. На всех информационных входах всех микросхем, за исключением логических элементов, присутствуют так называемые резисторы подтяжки (англ. «pull-up resistor»), которые обеспечивают поступление на вход микросхемы высокого уровня лог. «1» в случае, если вход микросхемы не задействован. Также в плате присутствуют некоторые дополнительные соединения, характерные для типичного способа использования той или иной микросхемы (см. ниже).

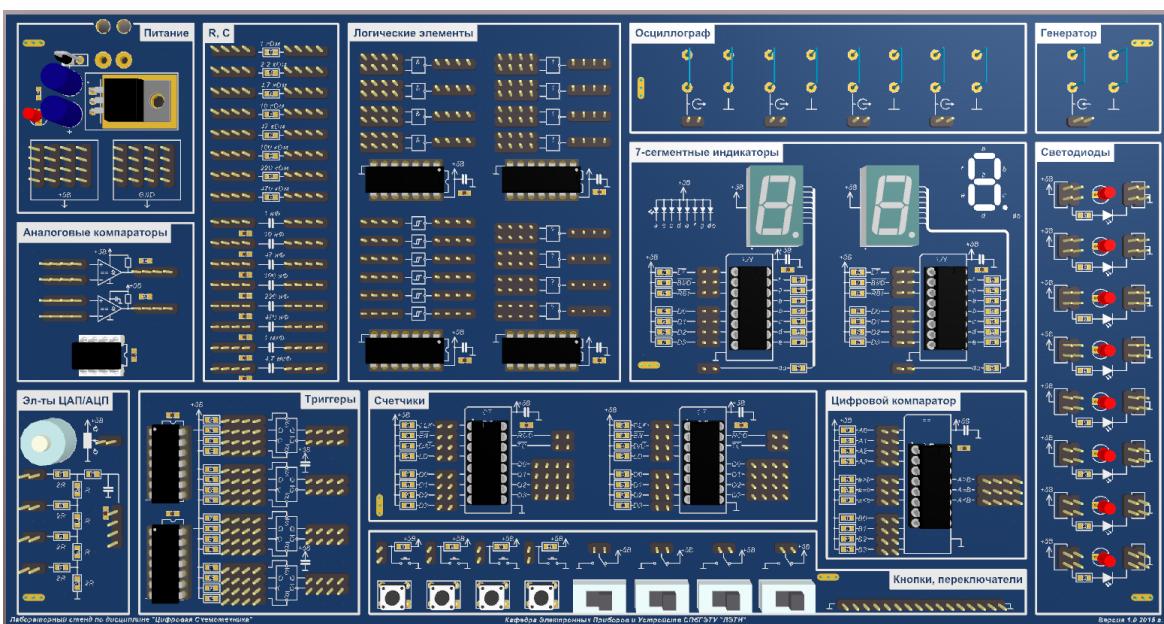

Внешний вид стенд показан на Рис. 1.

Рис. 1. Внешний вид стенд для выполнения лабораторных работ

Стенд разделен на ряд блоков, названия которых подписаны в рамках сверху.

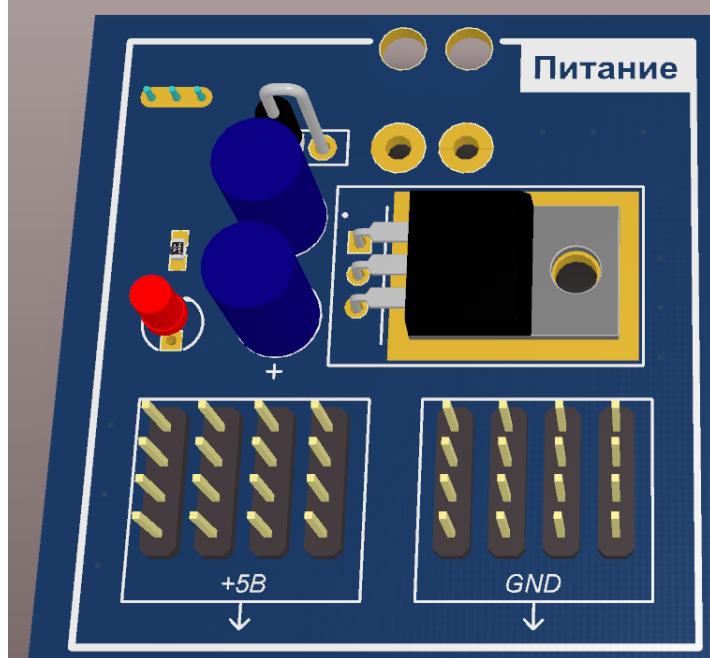

**Блок «Питание»** содержит точки подключения кабеля питания. Из стенда выходит кабель с двумя проводниками разных цветов («плюс» и «минус»). Номинальное напряжение питания стенда составляет 9 В. В стенде установлен линейный регулятор напряжения типа 7805, понижающий входное напряжение до уровня питания цифровых микросхем 5 В, а также защитный диод, исключающий выход элементов из строя при неправильной полярности подключения питающего кабеля.

Внешний вид блока показан на Рис. 2.

Рис. 2. Блок «Питание»

Наличие напряжения питания платы индицируется светодиодом.

Общие принципы работы с платой аналогичны описанному в методических указаниях по выполнению лабораторных работ дисциплины «Аналоговая Схемотехника». **Блоки «Осциллограф» и «Генератор»** в точности повторяют уже знакомые студентам технические решения; блок «Мультиметр» в плате отсутствует, т.к. мультиметр при выполнении лабораторных работ используется крайне редко.

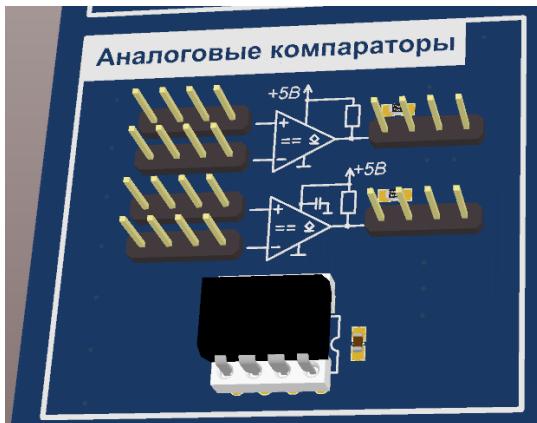

**Блок «Аналоговые компараторы»** функционально аналогичен одноименному блоку стенда «Аналоговая Схемотехника» и содержит микросхему LM393, представляющую собой сдвоенный компаратор с выходом типа «открытый коллектор» (см. Рис. 3).

Рис. 3. Блок «Аналоговые компараторы»

Ввиду того, что аналоговые компараторы в лабораторных стендах применяются в цифроаналоговых схемах с микросхемами ТТЛ-совместимых уровней, каждый из выходов

снабжен резистором-подтяжкой номиналом 10 кОм. Таким образом, выход каждого из компараторов можно напрямую подключить ко входу любой цифровой микросхемы без дополнительных элементов.

**Блок «R, С»** содержит набор резисторов и конденсаторов, которые используются в цифроаналоговых схемах мультивибраторов, одновибраторов и т.д., построенных на цифровых микросхемах. И резисторы, и конденсаторы имеют типоразмер 0603. В плате присутствует всего один элемент каждого номинала. Номиналы резисторов: 1, 2.2, 4.7, 10, 47, 100, 220, 470 кОм. Номиналы конденсаторов: 1, 10, 47, 100, 220, 470 нФ; 1, 4.7 мкФ. К каждому выводу элемента подключено по блоку из четырех штырьковых разъемов.

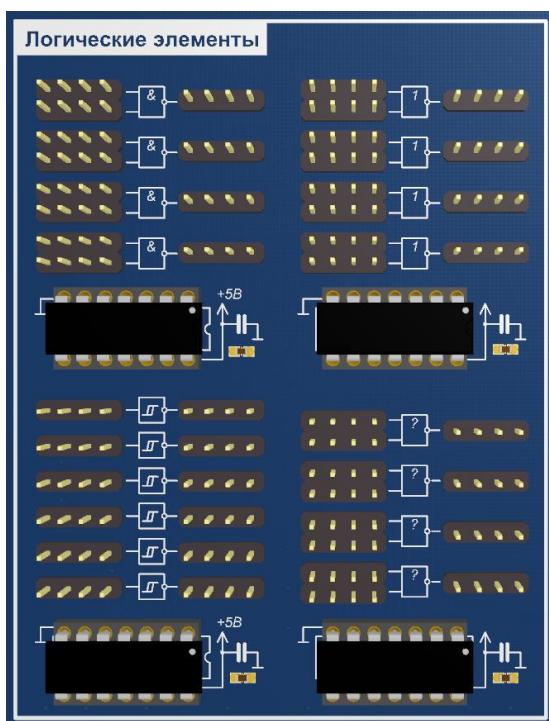

**Блок «Логические элементы»** (см. Рис. 4) содержит четыре интегральных микросхемы следующих типов:

1. 74HC14 – шесть инвертирующих триггеров Шмитта;

2. 74HC00 – четыре ЛЭ 2И-НЕ;

3. 74HC02 – четыре ЛЭ 2ИЛИ-НЕ;

4. Место для установки интегральной схемы, содержащей четыре двухвходовых ЛЭ со стандартной цоколевкой по выбору преподавателя.

Рис. 4. Блок «Логические элементы»

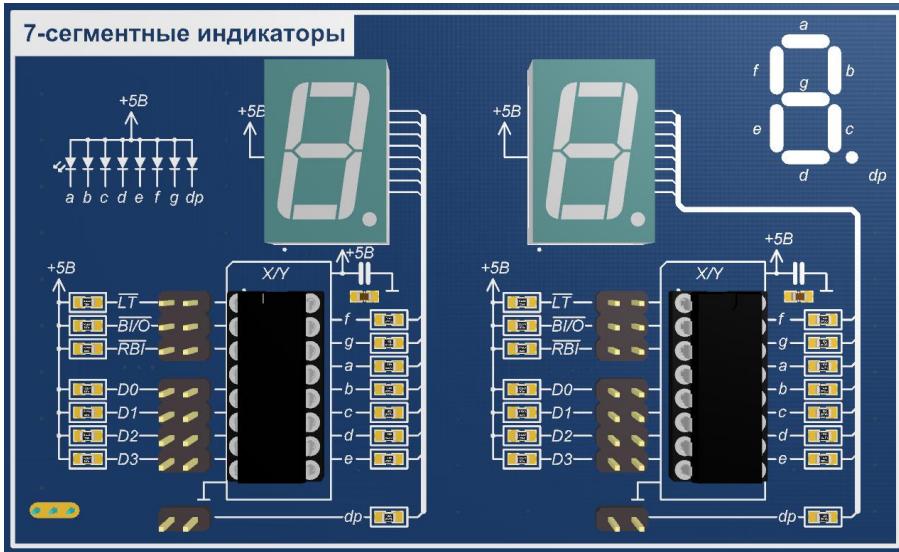

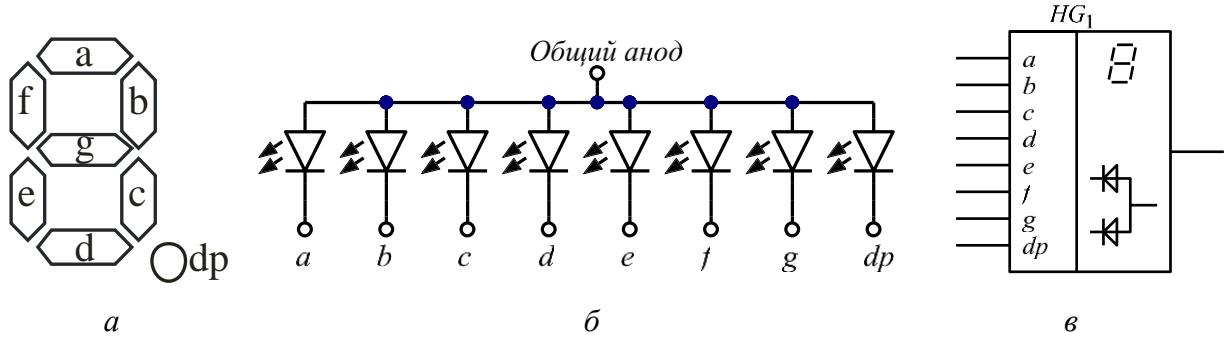

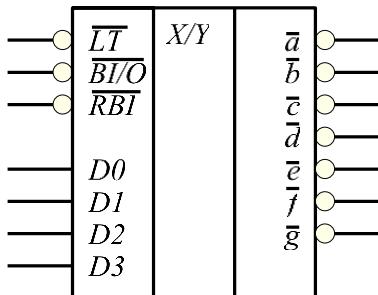

**Блок «Семисегментные индикаторы»** довольно сложен и содержит два светодиодных семисегментных индикатора с общим анодом, уже подключенных через токоограничительные резисторы (1 кОм) к дешифратору типа 74LS47. Данная микросхема осуществляет преобразование двоично-десятичного кода на входе в специфический код управления семисегментным индикатором на выходе так, что число, поданное на вход дешифратора, можно считать с соответствующего индикатора.

Помимо сегментов, которые служат для изображения арабских цифр, индикаторы содержат символы десятичного разделителя (точки). Светодиод, индицирующий десятичный разделитель, также подключен катодом к токоограничительному резистору, второй вывод которого подключается к блоку из двух штырьковых разъемов.

Внешний вид блока показан на Рис. 5. Как видно, плата стенда позволяет отображать числа в диапазоне 00-99 с опциональной десятичной точкой-разделителем в любой позиции. Внутренняя схемотехника индикаторов и общепринятые буквенные индексы сегментов показаны в виде рисунков.

Рис. 5. Блок «7-сегментные индикаторы»

Все входы дешифратора 74LS74 имеют резисторы подтяжки номиналом 10 кОм. Обращаем внимание, что данная микросхема – единственная в плате, выполненная по технологии ТТЛШ. Все остальные микросхемы серий НС(Т) ТТЛ-совместимы, но изготовлены по КМОП-технологии.

**Блок «Светодиоды»** (см. Рис. 6) содержит 8 индикаторных светодиодов, подключенных анодами к индивидуальным токоограничительным резисторам номиналом 1 кОм. Светодиоды могут быть включены как логическим уровнем «0», так и «1». В первом случае необходимо подключить резистор к источнику питания «+5В», а катод светодиода – к выходу какой-либо интегральной схемы. Если необходимо активировать индикатор уровнем лог. «1», то катод светодиода подключается к «земле», а резистор (к которому обращен анод) – к выходу интегральной схемы.

Рис. 6. Блок «Светодиоды» (фрагмент)

Для упрощения коммутации рядом со сдвоенными штырьковыми разъемами светодиода установлены разъемы, подключенные к цепям «+5В» и «GND». Это позволяет использовать вместо монтажного провода перемычки («джамперы»), которые выдаются преподавателем.

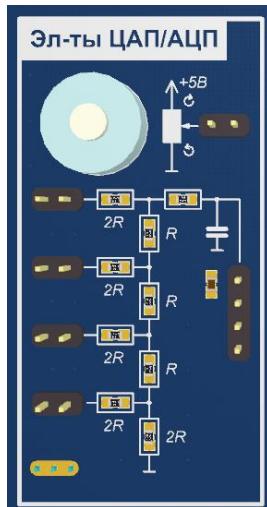

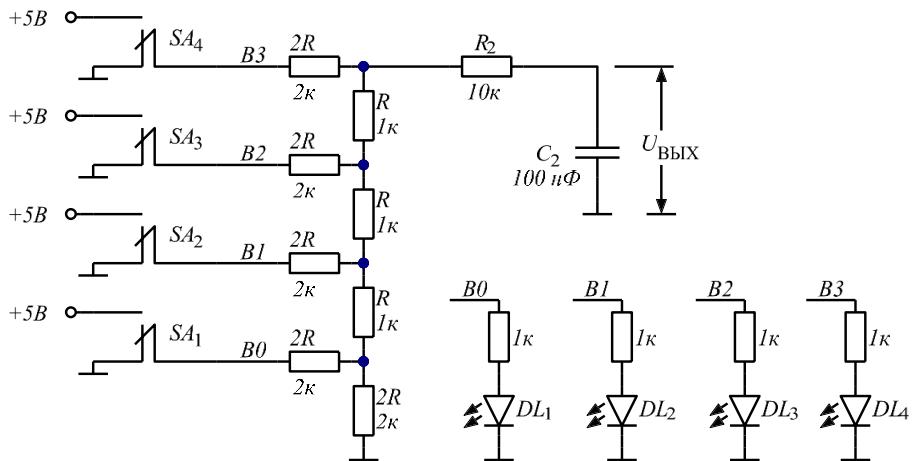

**Блок «Элементы ЦАП/АЦП»** содержит потенциометр типа СП-16ВА мощностью 0.25 Вт на полное сопротивление в несколько кОм (зависит от экземпляра платы). Крайние выводы потенциометра подключены к цепям питания, а скользящий контакт – к сдвоенному штырьковому разъему, с которого снимаются напряжения в диапазоне от 0 до 5 В. Направление

вращения движка потенциометра для увеличения и уменьшения этого напряжения показано рисунком на плате (см. Рис. 7).

Рис. 7. Блок «Элементы ЦАП/АЦП»

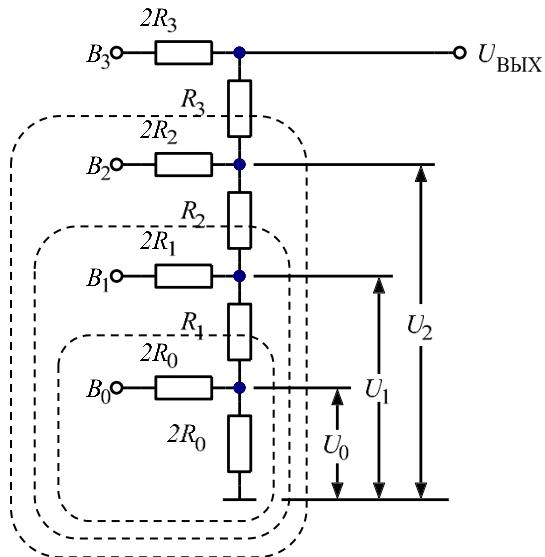

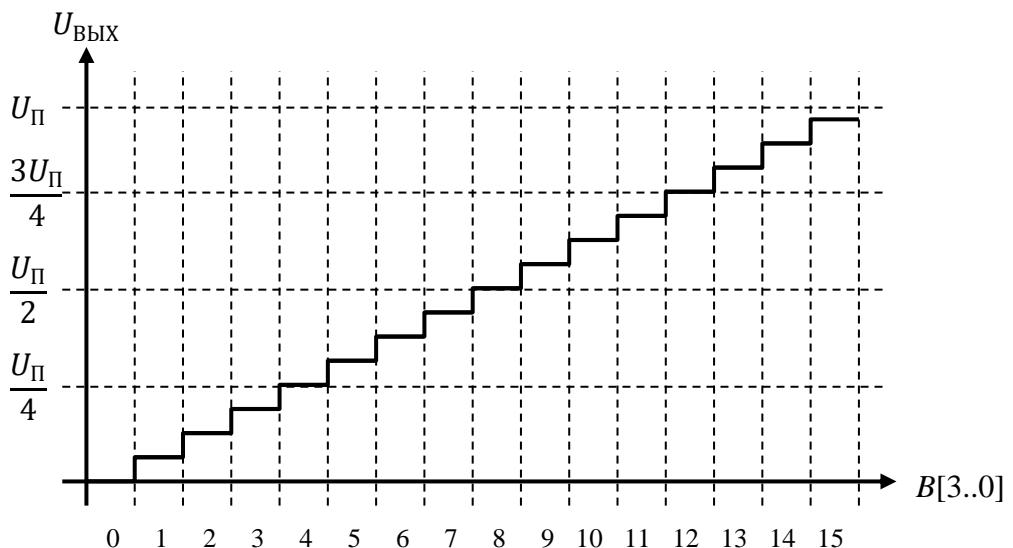

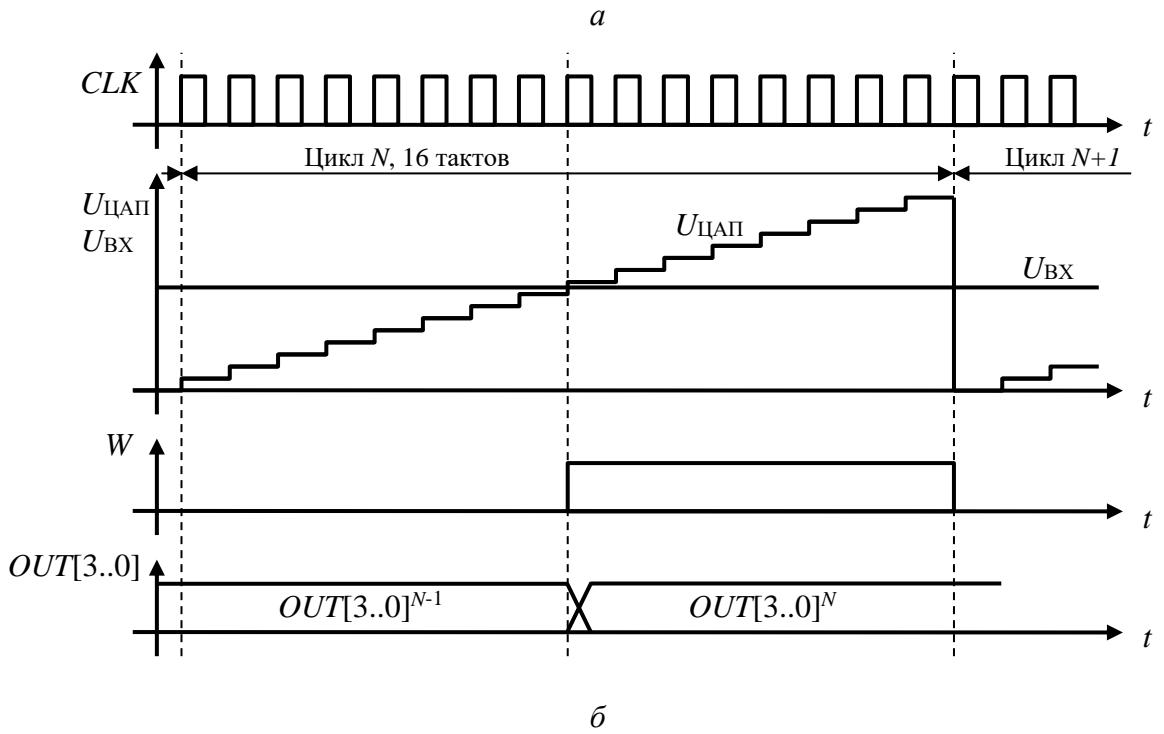

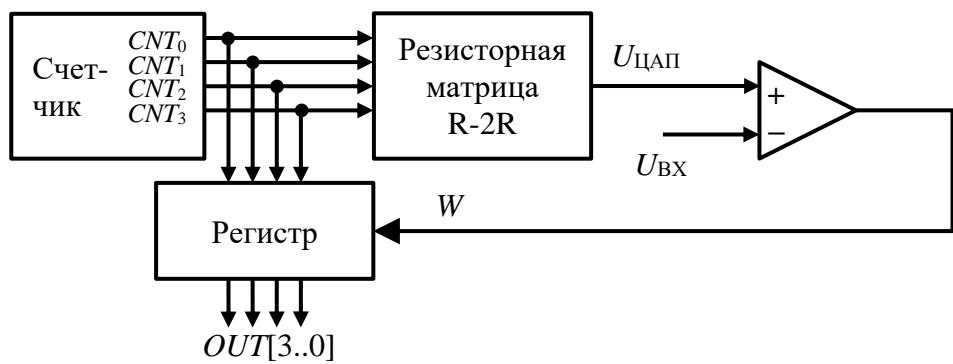

Под потенциометром собрана схема, представляющая собой 4-разрядную резистивную матрицу R-2R (англ. «Resistor ladder») на резисторах номиналом 1 и 2 кОм с выходным RC-фильтром 100 кОм, 1 нФ. Данная схема используется для построения и исследования простейшего ЦАП (цифроаналогового преобразователя). Входы и выходы матрицы подключены к штырьковым разъемам.

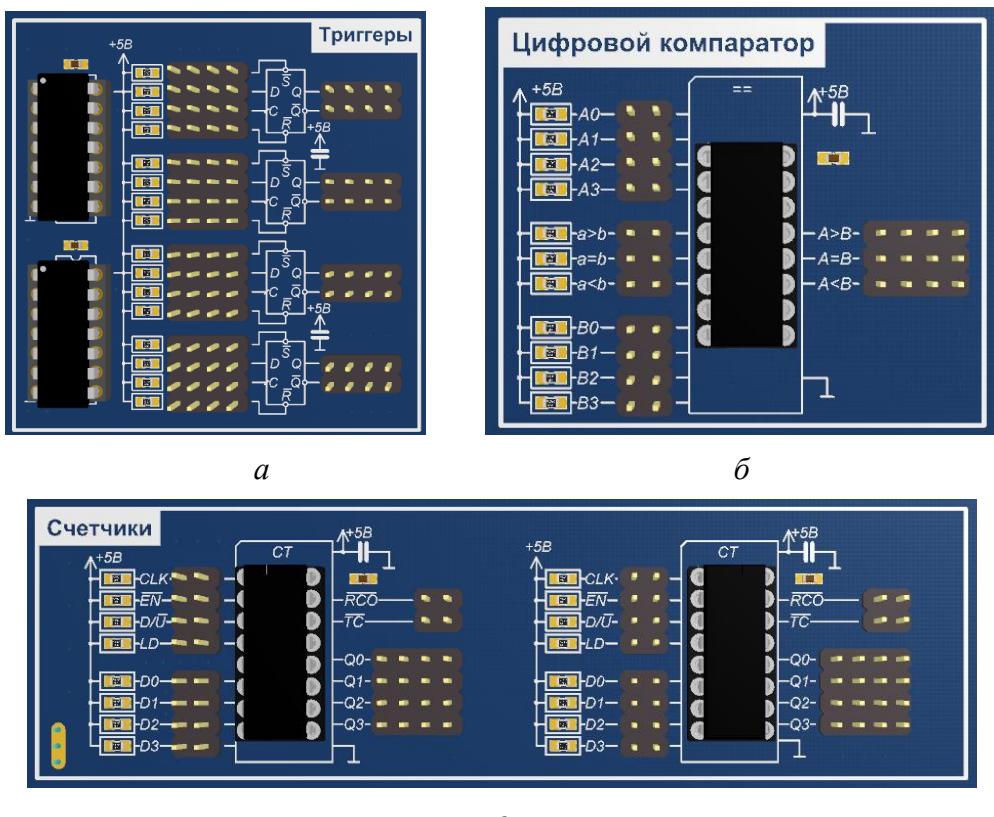

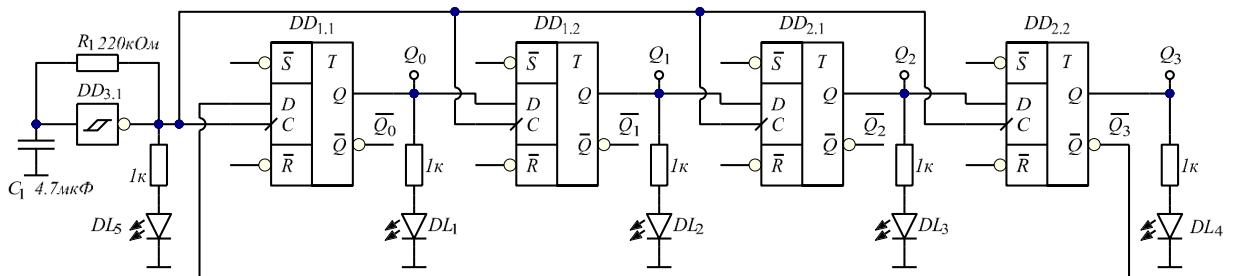

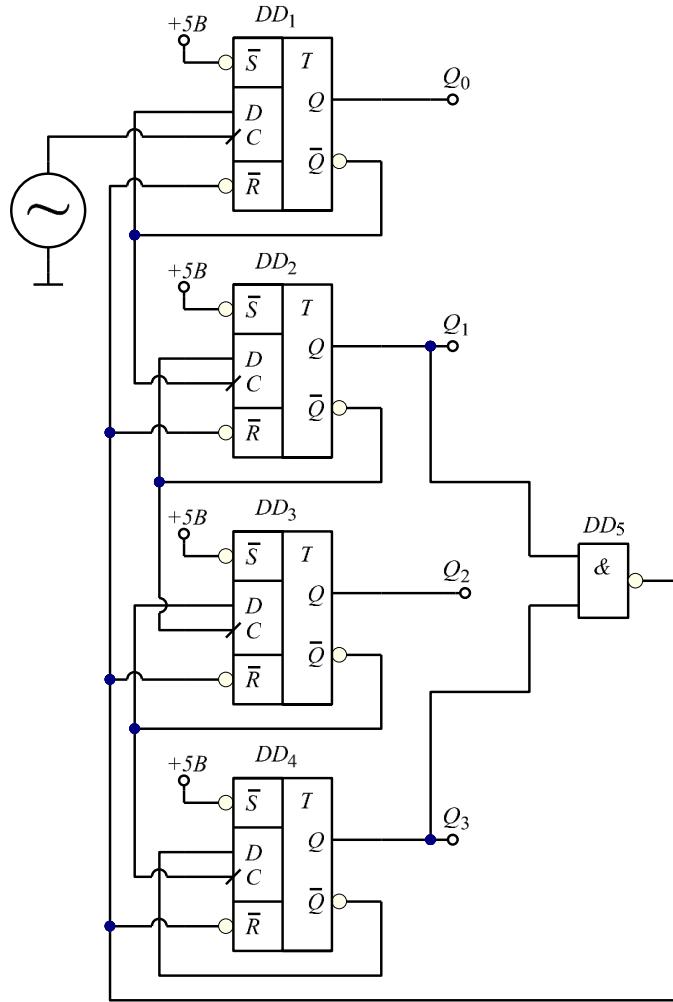

**Блок «Триггеры»** содержит две интегральные микросхемы, каждая из которых представляет собой пару универсальных RS/D-триггеров (D-триггеров с асинхронными установкой и сбросом) типа 74HC74. Все входы имеют встроенные резисторы подтяжки номиналом 10 кОм и штырьковые разъемы; для использования доступны оба выхода каждого из триггеров – прямой и инверсный (см. Рис. 8, а).

Рис. 8. Блоки «Триггеры» (а), «цифровой компаратор» (б) и «счетчики» (в)

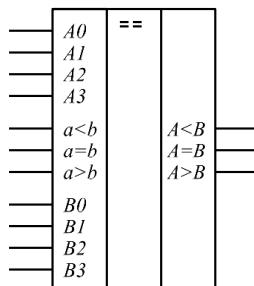

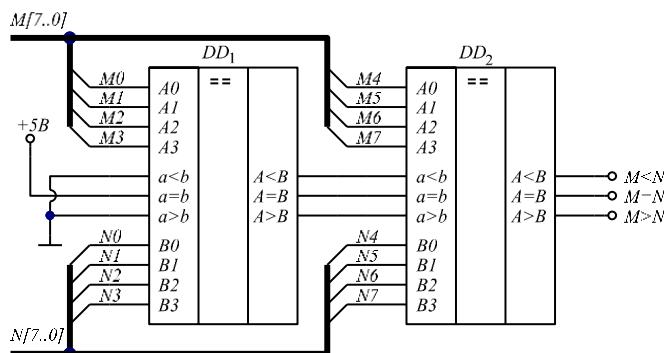

**Блок «Цифровой компаратор»** содержит микросхему типа 74HC85, которая позволяет осуществлять сравнение двух четырехразрядных чисел А и В и поддерживает каскадирование для увеличения разрядности. Все входы (как информационные, так и входы каскадирования) снабжены резисторами подтяжки (см. см. Рис. 8, б).

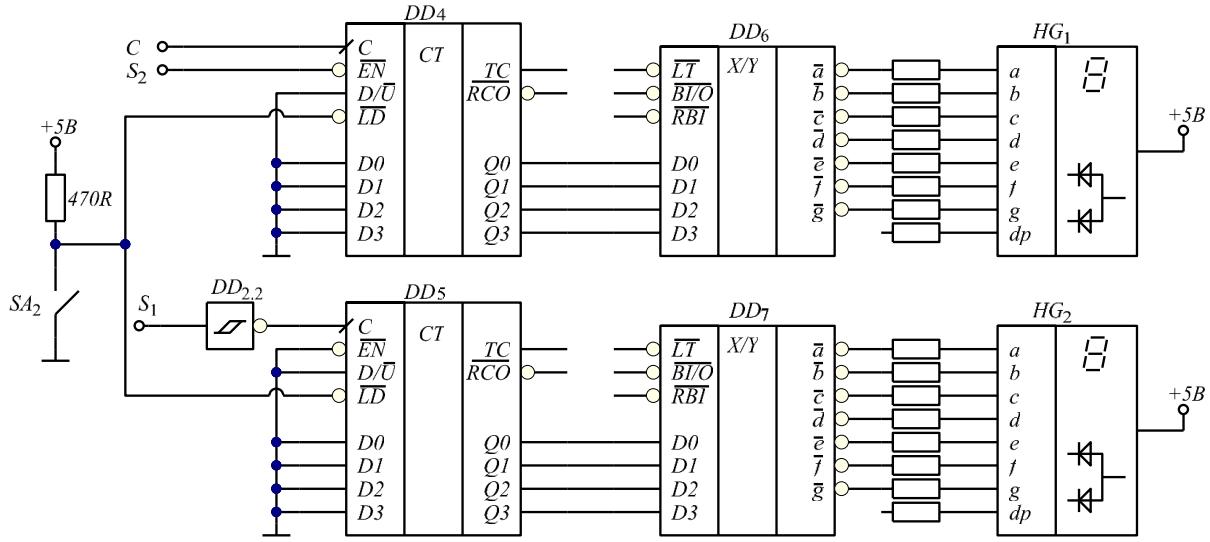

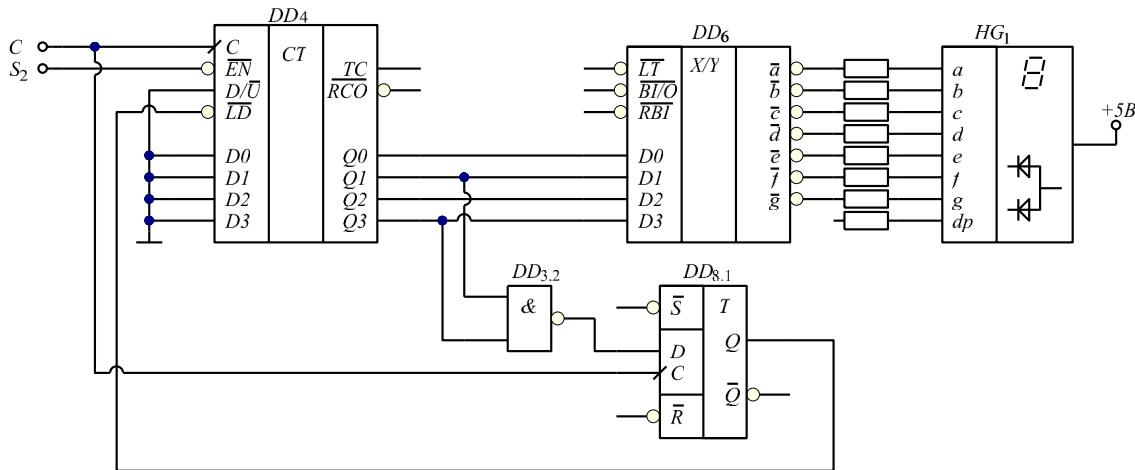

**Блок «Счетчики»** (см. Рис. 8, в) содержит два четырехразрядных реверсивных синхронных двоичных счетчика типа 74HC191. Счетчики имеют входы и выходы для каскадирования, функцию параллельной загрузки и функцию сброса.

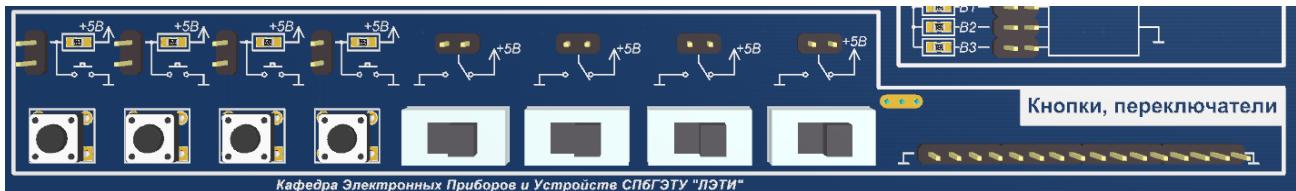

Для ввода цифровых данных в схему, собранную на плате, и ее настройки, служит **блок «Кнопки и переключатели»** (см. Рис. 9).

Рис. 9. Блок «Кнопки и переключатели»

Как видно, плата содержит 4 кнопки и 4 переключателя.

Схема включения кнопок благодаря наличию резисторов подтяжки такова, что с группы из двух штырьковых разъемов при не нажатой кнопке снимается уровень напряжения, соответствующий напряжению питания или лог. «1». Нажатая кнопка заземляет цепь штырьковых разъемов, и уровень напряжения падает до нуля (лог. «0»). Кнопки следует использовать в случаях, когда требуется вручную кратковременно менять логический уровень на каком-то входе схемы.

Переключатели не требуют резисторов подтяжки и, в зависимости от положения, подключают штырьковые разъемы либо к питанию (лог. «1»), либо к земле (лог. «0»). Переключатели следует использовать в случае, когда требуется иметь число или набор логических уровней, которые необходимо изменять время от времени в процессе настройки или исследования схемы.

Также описанный блок содержит ряд штырьковых разъемов, подключенных к «земле» (лог. «0»). Это ряд полезен для того, чтобы в процессе сборки схемы постоянно подключить какой-то вход микросхемы к уровню лог. «0». Для этого следует соединить с землей этот вход при помощи монтажного провода. При отсутствии такого подключения вход окажется, скорее всего, подключенным к уровню лог. «1», т.к. на подавляющем большинстве входов сложных цифровых микросхем в плате установлены резисторы подтяжки.

Все интегральные схемы установлены в цанговые панельки («кроватки»), которые обеспечивают быструю и удобную замену вышедшего из строя компонента без использования пайки.

Для выполнения конкретных лабораторных работ преподаватель выдает студентам дополнительные навесные компоненты, такие, как пьезокерамические излучатели звука, перемычки («джамперы») и т.д. Все они снабжены ответными частями штырьковых разъемов и могут быть подключены в любые узлы схемы.

### 1.2.2. Рекомендации по сборке электрических схем

Общие рекомендации по сборке электрических схем аналогичны изложенному в методических указаниях [АнСХТ].

Специфика цифровой схемотехники заключается в том, что чаще всего цифровые электрические схемы больше, и содержат большее количество элементов и соединений, нежели аналоговые. Для упрощения процесса сборки схем на плате, как видно, уже принят ряд мер (часть узлов заранее смотнированы). Исходя из специфики цифровой схемотехники, остается рекомендовать:

- Соблюдать порядок подключений шин и групп индикаторов. Например, для отображения состояния бит байта, следует подключать цепи битов к светодиодам по порядку и не сбиваясь: бит 0 – нижний светодиод, бит 1 – второй снизу, ... бит 7 – верхний светодиод. При организации ввода многоразрядного числа в схему также следует соблюдать порядок использования кнопок и переключателей. Например, бит 3 – слева, затем биты 2, 1, а бит 0 – справа.

- Использовать перемычку («джампер») везде, где можно заменить его монтажный провод. Например, для того, чтобы установить направление счета счетчика 74HC191 на увеличение и разрешить счет, требуется заземлить входы  $\overline{EN}$  и  $D/\overline{U}$ . При сборке схемы удобнее подключить монтажный провод, соединенный с землей, например, к  $D/\overline{U}$ , а затем установить перемычку между  $D/\overline{U}$  и  $\overline{EN}$ .

- В случае, когда требуется наблюдать медленно изменяющиеся сигналы (логические уровни), вместо осциллографа удобно использовать любой из доступных светодиодов.

- Для наблюдения быстро изменяющихся сигналов используется осциллограф. Если сигналы периодические, осциллограф используется так же, как и при исследовании аналоговых схем мультивибраторов, компараторов, усилителей сигнала, поступающего с лабораторного генератора. Если сигналы апериодические (например, реакция схемы на нажатие какой-то кнопки), рекомендуется освоить и применять специфические режимы синхронизации осциллографа: режим синхронизации «Normal» с автоматической блокировкой обновления экрана без событий синхронизации, режим съемки одного кадра «Single seq.», выбор фронта синхронизации.

- При осциллографировании группы периодических синхронизированных друг с другом сигналов, в качестве источника синхронизации следует выбирать самый «медленный» из них, например, старший бит на выходе счетчика при съемке всех четырех его выходных битов.

- В подавляющем большинстве случаев необходимо и достаточно выбрать такой масштаб каналов по оси Y осциллографа, чтобы одна клетка на экране соответствовала логическому перепаду (5 В). Самы каналы при этом следует разнести так, чтобы осциллограммы не пересекались.

### 1.3. Основные теоретические сведения

Цифровая схемотехника на уровне составления электрических принципиальных схем, если речи не идет об особых случаях, оперирует не электрическими физическими величинами (ток, напряжение и т.д.), а логическими уровнями. Сигналы, распространяющиеся по цепям таких схем, являются цифровыми, т.е. напряжения в этих цепях могут принимать лишь два значения – уровень логического нуля и уровень логической единицы.

В зависимости от технологии изготовления использованных в схеме интегральных микросхем, физические определения понятий «лог. 1/0» разнятся. Исторически первый массовой серией интегральных цифровых микросхем являются микросхемы транзисторно-транзисторной логики (ТТЛ), построенные на биполярных транзисторах и питающиеся напряжением 5 В. У этих микросхем имелся ряд недостатков, связанных с их невысоким быстродействием и значительным потреблением, вследствие чего в настоящий момент они используются крайне редко. Однако наиболее популярные сегодня серии цифровых интегральных микросхем (74HC/HCT), хоть и выполнены по КМОП-технологии (в основе которой лежат полевые транзисторы с p- и n-каналом), но являются ТТЛ-совместимыми, т.е. работают с такими напряжениями лог. «0» и «1», которые могут быть созданы и корректно восприняты устаревшими ТТЛ-микросхемами.

Если сильно упростить, то уровень лог. «1» для таких микросхем составляет порядка  $U_P$  или 5 В, а уровень лог. «0» порядка 0 В. Полное же описание физического уровня того или иного интерфейса логических интегральных схем, конечно, задает логические уровни в виде диапазона напряжений, описывает временные параметры процесса смены логического уровня в цепи и т.д. и т.п.

Сама суть цифрового сигнала следует из ограничений, которые на него изначально накладываются. Одна цепь несет информацию бинарного вида – «истина/ложь», «да/нет», «готов/не готов», «открыто/закрыто», «о.к./ошибка». Если ряд цифровых сигналов объединить и условно пронумеровать, то полученная шина позволит записывать и передавать двоичные числа. Поскольку сигнал в одной цепи принимает лишь два значения (0, 1), то количество комбинаций уровней сигналов в шине из двух цепей составит 4 (00, 01, 10, 11), из трех – восемь (000...111) и т.д. Полученное *двоичное* число может быть обработано более сложными цифровыми узлами, от сравнительно простых устройств сложения и сравнения до универсальных арифметико-логических устройств. Вместе с тем, все эти устройства, включая сложнейшие современные микропроцессоры, строятся из простых логических элементов (ЛЭ) в интегральном исполнении. Исследованию ЛЭ, выпущенных как компоненты в виде отдельных интегральных микросхем, и посвящена данная вводная лабораторная работа.

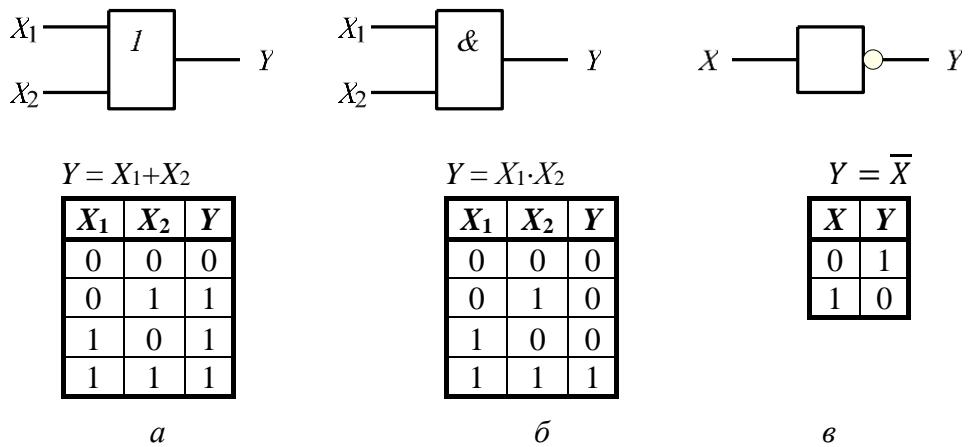

ЛЭ сами по себе могут как быть частью более сложных схемотехнических блоков, так и выполнять самостоятельные функции. Рассмотрим простейший наглядный пример с сигнализацией, оснащенной двумя датчиками, высокий логический уровень на выходе каждого из которых соответствует ситуации «тревога». Сирена будет включена, если хотя бы с одного из датчиков поступит высокий уровень. Т.е. сигнализация работает по алгоритму «включить сирену, если с датчика №1 ИЛИ с датчика №2 поступил уровень лог. «1». Если сирена включается высоким уровнем напряжения, описанный алгоритм реализуется одним логическим элементом типа ИЛИ (англ. OR). Таблица, описывающая уровень на выходе такого ЛЭ для всех комбинаций сигналов на входах, также называемая *таблицей истинности*, показана на Рис. 10, а.

Рис. 10. ЛЭ типа ИЛИ (а), И (б), НЕ (в)

Описывать поведение ЛЭ иногда удобнее не таблицей, а выражением *алгебры логики*, похожим на обычное алгебраическое. Для ЛЭ типа ИЛИ операция, которую он выполняет (*дизъюнкция*), описывается соотношением  $Y = X_1 + X_2$ . Ввиду того, что и  $X_{1,2}$ , и  $Y$  могут принимать лишь два значения (0 и 1), корректность таблицы, показанной на Рис. 10, а, очевидна ( $0+0=0$ ,  $0+1=1$ ,  $1+0=1$ ,  $1+1=1$  т.к. уровня «2» не существует).

Аналогично можно описать элемент И (англ. OR), см. Рис. 10, б. Напряжение на его выходе примет уровень лог. «1», если на обоих входах уровни составляют лог. «1», т.е.  $Y = 1$  если  $X_1 = 1$  И  $X_2 = 1$  (см. Рис. 10, б). На языке алгебры логики такое поведение описывается выражением  $Y = X_1 \cdot X_2$ , что также интуитивно согласуется с простейшей алгеброй, и называется *конъюнкцией*.

Третий базовый ЛЭ называется логическим НЕ, или *инвертором*, а операция, соответственно, *инверсией*. Если на вход такого элемента поступает сигнал  $X = 1$ , то на выходе формируется уровень  $Y = 0$ ; низкий уровень сигнала на входе  $X = 0$  дает высокий уровень на выходе  $Y = 1$ . Таблица истинности, условное графическое обозначение (УГО) и выражение на языке алгебры логики показаны на Рис. 10, в.

Очевидно, что подвергнуть операции сложения или умножения (дизъюнкции / конъюнкции) можно не только два, но также три и более операнда. Имея только ЛЭ с двумя входами, можно использовать второй такой ЛЭ, тогда на примере логической операции ИЛИ можно записать  $Y_1 = X_1 + X_2$ ,  $Y_2 = Y_1 + X_3$ , т.е.  $Y_2 = X_1 + X_2 + X_3$ . Электронная промышленность выпускает ЛЭ с тремя и более входами. Для того чтобы обозначить в названии ЛЭ число его входов, часто пишут «3И», «4ИЛИ» и т.д. Инвертора с более чем одним входом, очевидно, не существует.

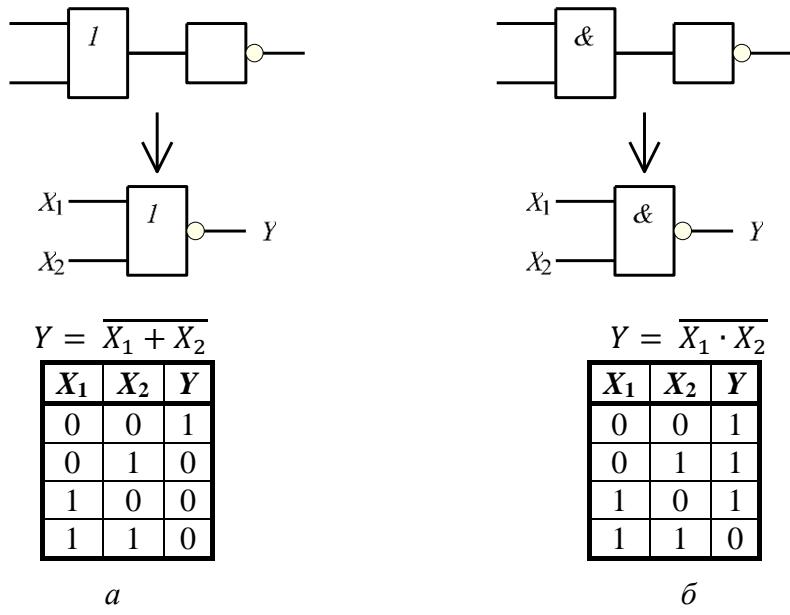

Ввиду большей гибкости при составлении сложных логических схем, имеющих много входов и выходов, особую популярность приобрели так наз. *универсальные ЛЭ* в интегральном исполнении. Универсальные ЛЭ отличаются от простейших И/ИЛИ тем, что результат сложения/умножения дополнительно инвертируется (см. Рис. 11). В полном названии универсального логического элемента появляется, соответственно, указание на инверсию результата. Так возникают названия формата 2И-НЕ (англ. 2-input NAND), 4ИЛИ-НЕ (4-input NOR).

Рис. 11. Универсальные ЛЭ типа 2ИЛИ-НЕ (а) и 2И-НЕ (б)

Теория алгебры логики показывает, что имея лишь универсальные ЛЭ одного типа, можно построить как любые ЛЭ другого типа, так и вообще, теоретически, любое цифровое устройство. В частности, согласно законам Де Моргана,

$$(1) \quad \overline{X_1 + X_2} = \overline{X_1} \cdot \overline{X_2} \text{ и } \overline{X_1 \cdot X_2} = \overline{X_1} + \overline{X_2}.$$

Допустим, в наличии имеются только ЛЭ типа 2И-НЕ, и требуется построить ЛЭ типа ИЛИ. Элемент 2И-НЕ можно использовать как инвертор, закоротив его входы (т.к.  $\overline{X_1 \cdot X_1} = \overline{X_1}$ ). Далее, проинвертировав левую и правую части первого соотношения (1), получим:

$$X_1 + X_2 = \overline{\overline{X_1} \cdot \overline{X_2}}.$$

Полученное соотношение описывает реализацию ЛЭ типа ИЛИ на универсальных ЛЭ ИЛИ-НЕ. На языке схемотехники полученное преобразование можно изобразить в виде схемы следующим образом:

Рис. 12. Реализация ЛЭ типа ИЛИ на универсальных ЛЭ ИЛИ-НЕ

В корректности созданной схемы можно легко убедиться и не используя формальный аппарат алгебры логики. Допустим, хотя бы один из входов схемы, показанной на Рис. 12, т.е.  $X_1$  или  $X_2$ , оказывается равным логической единице. Это означает, что после инверсии на вход ЛЭ DD3 поступит как минимум один уровень лог. «0». В результате выполнения операции И в DD3 формируется логический ноль, который после инверсии (логический элемент – универсальный) дает лог. «1» на выходе. Иными словами, полученная схема реализует таблицу истинности ЛЭ типа 2ИЛИ.

Логические элементы используются для построения, в том числе, комбинаторных узлов, как в интегральном исполнении (в виде интегральных микросхем) так и в виде обычных схем.

Комбинаторные узлы – схемы, имеющие некоторое количество входов и выходов, и при этом состояния выходов определяются мгновенно и исключительно текущим состоянием входов (т.е. комбинаторные схемы не имеют свойства запоминать и хранить данные). Существует большое количество типовых комбинаторных узлов – дешифраторы и шифраторы, демультиплексоры и мультиплексоры, сумматоры, компараторы и т.д. Как правило, такие узлы имеют группы входов, логические уровни которых интерпретируются как двоичные числа. Разрядность чисел соответствует числу входов, объединенных в группу.

**Компараторы** служат для сравнения групп логических сигналов (чисел). Компараторы имеют два многоразрядных входа  $A[n..0]$  и  $B[n..0]$  и выходы:  $A < B$ ,  $A = B$ ,  $A > B$  (при этом разрядность входных чисел составляет  $n+1$ ). Уровень лог. «1» на одном из выходов показывает, как соотносятся числа  $A$  и  $B$ . Схемы компараторов могут иметь входы для каскадирования, т.е. увеличения разрядности всей схемы за счет соединения в цепочки нескольких микросхем или схем меньшей разрядности.

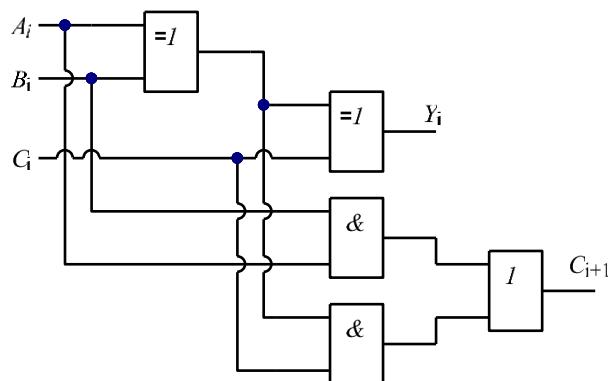

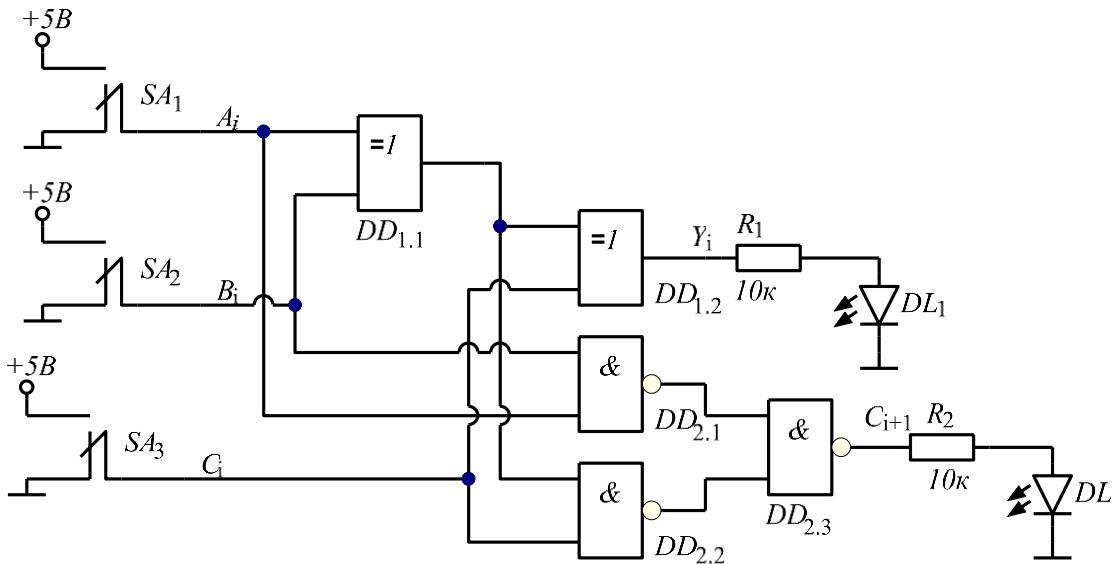

**Сумматоры** служат, как следует из названия, для сложения чисел. Многоразрядный сумматор, в т.ч., в интегральном исполнении, состоит из цепочки одноразрядных сумматоров – несложных схем, которые способны складывать одноразрядные числа.

Алгоритм работы сумматора не сложнее алгоритма сложения чисел «в столбик». Для младшего бита в каскаде справедливо:  $0 + 0 = 0$ ,  $0 + 1 = 1$ ,  $1 + 0 = 1$ ,  $1 + 1 = 0$  с переносом в старший разряд. Следующие по старшинству одноразрядные сумматоры в каскаде имеют вход переноса и реализуют таблицу истинности, показанную на Рис. 13, а.

Здесь:  $A_i$ ,  $B_i$  –  $i$ -ые биты *операндов* сложения  $A$  и  $B$ ,  $C_i$  – вход переноса  $i$ -того сумматора,  $C_{i+1}$  – выход переноса  $i$ -того сумматора в старший разряд (подключается ко входу переноса следующего по старшинству одноразрядного сумматора). Одноразрядный сумматор, не имеющий входа переноса, немного проще, и работает согласно первой половине таблицы истинности Рис. 13, а. Такой сумматор называется полусумматором.

| № строки | $A_i$ | $B_i$ | $C_i$ | $Y$ | $C_{i+1}$ |

|----------|-------|-------|-------|-----|-----------|

| 1        | 0     | 0     | 0     | 0   | 0         |

| 2        | 0     | 1     | 0     | 1   | 0         |

| 3        | 1     | 0     | 0     | 1   | 0         |

| 4        | 1     | 1     | 0     | 0   | 1         |

| 5        | 0     | 0     | 1     | 1   | 0         |

| 6        | 0     | 1     | 1     | 0   | 1         |

| 7        | 1     | 0     | 1     | 0   | 1         |

| 8        | 1     | 1     | 1     | 1   | 1         |

*a*

*б*

Рис. 13. Таблица истинности сумматора со входом переноса (а) и его реализация на ЛЭ (б)

Схемотехническая реализация сумматора удобна при использовании логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Такой ЛЭ не является базовым и реализует выражение  $Y = X_1\bar{X}_2 + \bar{X}_1X_2$ . Он работает, фактически, простейшим устройством сравнения битов:  $Y = 1$  если  $X_1 \neq X_2$ . Если биты на входе разные, то одно из слагаемых в выражении для ЛЭ примет значение лог. «1» и все выражение окажется равным единице. Если же биты одинаковые (два нуля или две единицы), то каждое из слагаемых в выражении даст лог. «0», чему и окажется равен результат  $Y$ . В этом нетрудно убедиться, подставив все возможные комбинации  $X_1$  и  $X_2$  в выражение для ЛЭ ИСКЛЮЧАЮЩЕЕ ИЛИ. Заметим, что у такого ЛЭ есть полезное свойство: лог. «1» на входе  $X_1$  приводит к появлению на выходе инвертированного уровня со второго входа  $X_2$ , (т.е. при  $X_1 = 1$   $Y = \bar{X}_2$ ) а при  $X_1 = 0$   $Y = X_2$ . Естественно, входы  $X_1$  и  $X_2$  у этого ЛЭ тождественны.

Для синтеза схемы сумматора можно и нужно использовать формальный подход: методы СКНФ или СДНФ (совершенные конъюнктивная и дизъюнктивная нормальные формы), математический аппарат для упрощения выражений алгебры логики. Однако, в принципе, такая схема может быть синтезирована и просто на основе таблицы истинности и понимания цифровой схемотехники.

Так, из строк 1-4 таблицы истинности (см. Рис. 13, а) следует, что при нулевом значении на входе переноса ( $C_i = 0$ ), выход сумматора  $Y_i$  устанавливается в единицу, если значения  $A_i$  и  $B_i$  – разные. При  $C_i = 1$  ситуация обратная (строки 5 и 8):  $Y_i = 1$  если  $A_i$  и  $B_i$  одинаковы. Иными словами, величину  $Y_i$  для сумматора можно сформировать двумя ЛЭ ИСКЛЮЧАЮЩЕЕ ИЛИ (см. Рис. 13, б): первый реализует строки 2 и 3 таблицы истинности, а второй, согласно его полезному свойству, описанному выше, инвертирует результат работы первого при установленном в единицу бите  $C_i$ , реализуя строки 5 и 8.

Для формирования сигнала переноса в старший разряд ( $C_{i+1}$ ) заметим: перенос устанавливается в 1, если  $A_i$  и  $B_i$  равны 1 вне зависимости от  $C_i$  (строки 4 и 8) или если  $A_i \neq B_i$  и при этом  $C_i = 1$  (строки 6 и 7). ЛЭ, выполняющий действие  $A_i \neq B_i$ , у нас уже есть в схеме формирования выходного бита; осталось добавить элементы типа И, ИЛИ, которые, фактически, соответствуют аналогичным предлогам русского языка (выделено курсивом в предыдущем предложении). Итоговая схема показана на Рис. 13, а.

**Дешифраторы и шифраторы** – цифровые комбинаторные узлы, схожие по строению с мультиплексорами и демультиплексорами. Они осуществляют преобразование кодов. В частности, дешифратор получает на вход двоичное число, представленное группой битов  $X[n...0]$  и формирует на выходе число, представленное группой битов  $Y[m...0]$ . Если разрядность входного двоичного числа  $N$  равняется  $n + 1$ , то разрядность выходного числа  $M$  составит  $2^N$ , так как число  $M$  – не двоичное число, а одноединичный код, соответствующий входному числу. В таком коде среди всех битов установлен всего один, остальные биты – нулевые. Позиция, в которой установлена единица, соответствует входному числу дешифратора  $X$ . Если  $X = 0$ , в числе  $M$  будет присутствовать единица только в бите 0, если  $X = 1$  в бите 1 и так далее. Поскольку число комбинаций, которые можно записать, имея  $N$  бит, составляет  $2^N$ , для кода  $Y$  потребуется столько же бит.

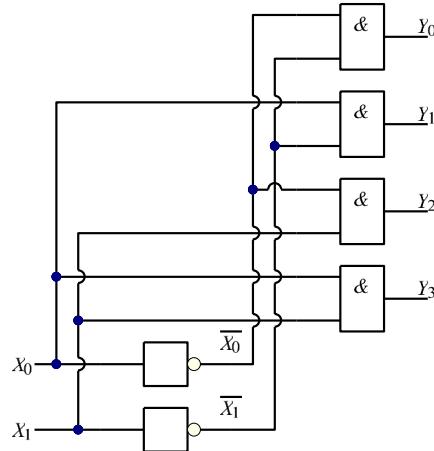

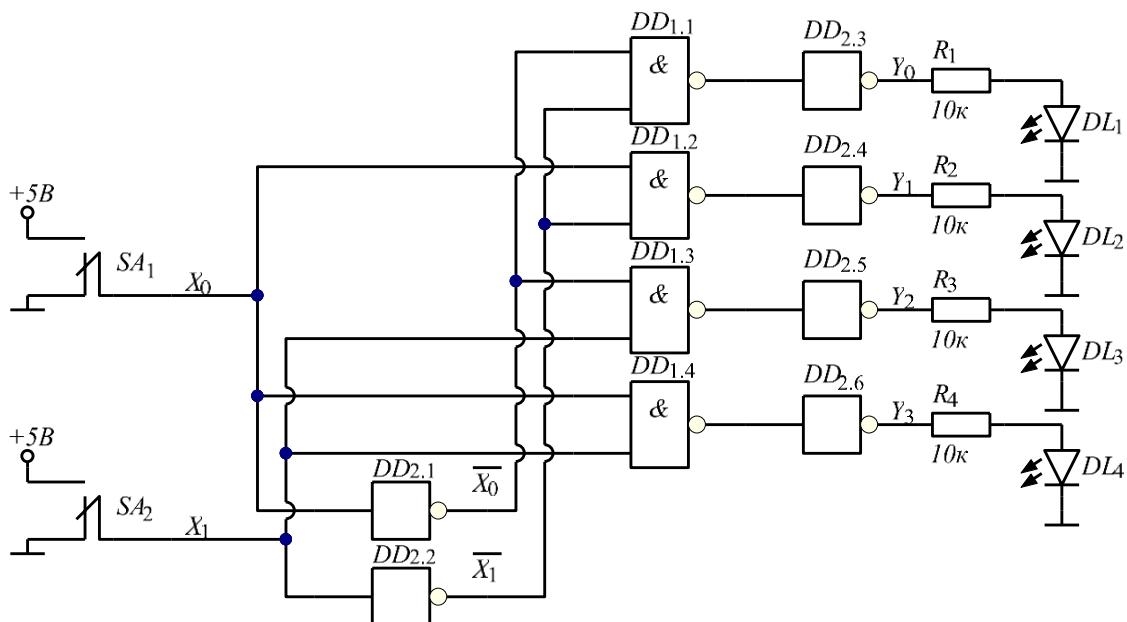

Таблица истинности дешифратора с двумя входами и четырьмя выходами показана на Рис. 14, а, а его реализация на ЛЭ – на Рис. 14, б.

| $X_1$ | $X_0$ | $Y_3$ | $Y_2$ | $Y_1$ | $Y_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 1     | 0     | 0     |

| 1     | 1     | 1     | 0     | 0     | 0     |

*a*

*б*

Рис. 14. Таблица истинности дешифратора «2 в 4» (а) и его реализация на ЛЭ (б)

Реализацию дешифратора на ЛЭ можно элементарно составить, проанализировав таблицу истинности и записав для каждой его строки простое выражение алгебры логики. Очевидно, что  $Y_0 = \bar{X}_0 \cdot \bar{X}_1$ ,  $Y_1 = X_0 \cdot \bar{X}_1$ ,  $Y_2 = \bar{X}_0 \cdot X_1$  и  $Y_3 = X_0 \cdot X_1$ . Для получения инвертированных значений входных битов в схеме задействовано два элемента НЕ, а для формирования выходного одноединичного кода, соответственно, четыре ЛЭ типа 2И.

Электронная промышленность выпускает, главным образом, интегральные схемы, содержащие более одного ЛЭ в корпусе. В частности, в плате лабораторного стенда установлены микросхемы, содержащие по 4 двухвходовых ЛЭ (англ. quad 2-input NAND / NOR gate) и 6 инверторов (англ. hex inverters). Такой подход, принятый в промышленности изначально, позволял уменьшать размеры электронных устройств, т.к. в схемах чаще всего требовалось несколько ЛЭ каждого типа. Однако после начала широкого распространения микропроцессорной техники и снижения уровня востребованности ЛЭ в приборостроении, появилась и развивается обратная тенденция – к выпуску компонентов со всего одним ЛЭ в сверхкомпактном корпусе.

## 1.4. Задание на проведение лабораторной работы

1. Подключите плату стенда (если она еще не подключена) к выходу «9В» лабораторного блока питания, соблюдая следующую полярность:

- $+9B$  – красный провод;

- «GND» – черный провод

Включите блок питания, убедитесь в том, что индикатор питания платы зажегся.

2. Соберите схему для исследования таблицы истинности любого из четырех доступных на плате ЛЭ типа 2И-НЕ (74HC00). Для этого:

- Подключите к выходу ЛЭ любой из светодиодов: катод светодиода подключите к «земле» при помощи перемычки, а анод, через встроенный токоограничивающий резистор – к выходу ЛЭ при помощи монтажного провода. Высокий уровень напряжения на выходе ЛЭ включит светодиод.

- Подключите к обоим входам ЛЭ по переключателю. Порядок расположения переключателей не имеет значения, т.к. входы используемых ЛЭ тождественны.

- Подключите еще два светодиода к штырьковым разъемам переключателей (и, соответственно, ко входам ЛЭ) аналогичным образом – высокий уровень напряжения на входе ЛЭ должен включать светодиод.

Полученная схема имеет следующий вид:

*Рис. 15. Схема для исследования таблицы истинности ЛЭ типа 2И-НЕ*

3. Снимите таблицу истинности ЛЭ типа 2И-НЕ, перебрав при помощи переключателей  $SA_{1,2}$  все возможные комбинации логических уровней на входе ЛЭ. Очевидно, их число составит 4, а таблица, соответственно, будет иметь следующий вид:

*Таблица 1. Формат таблицы истинности ЛЭ с двумя входами*

| $X_1$ | $X_2$ | $Y$ |

|-------|-------|-----|

| 0     | 0     |     |

| 0     | 1     |     |

| 1     | 0     |     |

| 1     | 1     |     |

Согласно схеме низкий логический уровень любой из цепей будет индицироваться выключенным светодиодом, а высокий – включенным. Какой из переключателей считать источником сигнала  $X_1$ , а какой –  $X_2$ , не имеет значения, т.к. входы ЛЭ тождественны. Важно не менять условного смысла переключателей в ходе эксперимента. Записывайте низкий логический уровень входных цепей  $X_{1,2}$  и выходной  $Y$  как «0», а высокий – как «1».

4. Переподключив монтажные провода, снимите таблицу истинности еще двух элементов: ЛЭ типа 2ИЛИ-НЕ (74HC02) и интегральной схемы, тип которой не обозначен на плате. Тип этой интегральной схемы заранее неизвестен и его требуется определить самостоятельно, обратившись к описанию данной лабораторной работы.

5. В отчете по лабораторной работе сравните таблицы истинности исследованных ЛЭ с известными теоретически соотношениями алгебры логики, описывающими их работу.

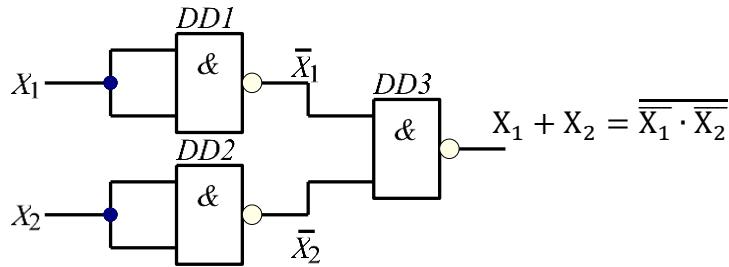

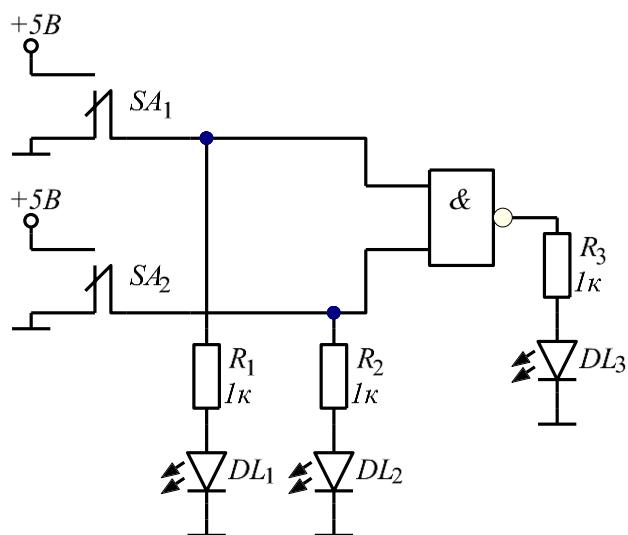

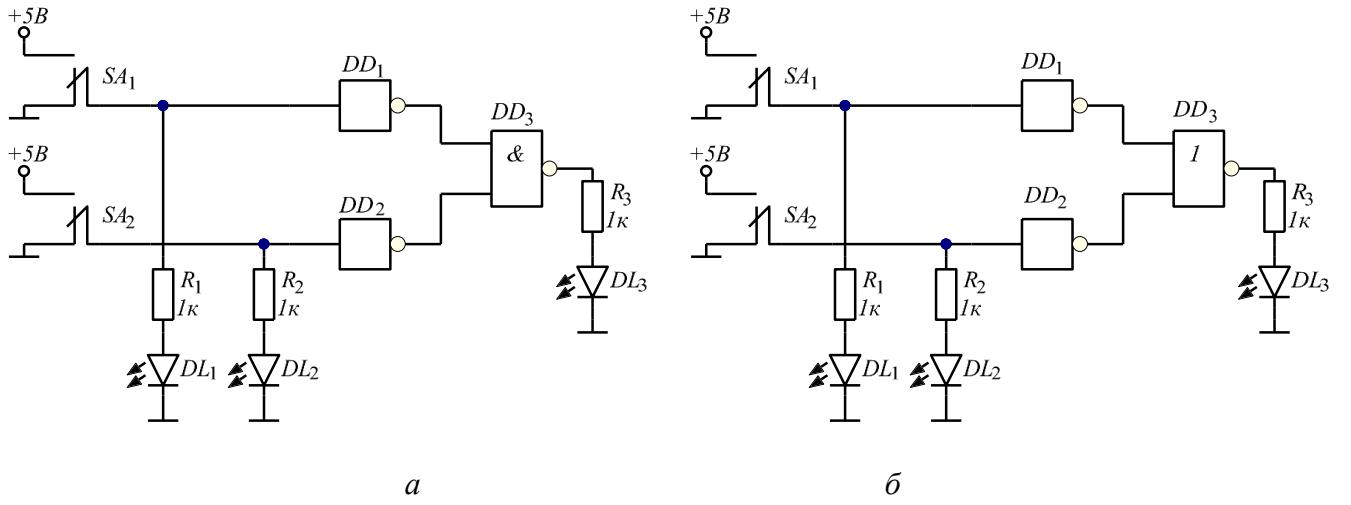

6. Соберите схему, демонстрирующую реализацию ЛЭ на универсальных ЛЭ другого типа, и исследуйте ее таблицу истинности. Бригады с **четными** номерами собирают схему, реализующую функцию ИЛИ на ЛЭ 2И-НЕ (Рис. 16, а), с **нечетными** – функцию И на ЛЭ типа 2ИЛИ-НЕ (Рис. 16, б). В целях упрощения сборки схемы для инвертирования сигналов ( $DD_{1,2}$ ) используйте не универсальные ЛЭ того же типа, что и  $DD_3$ , а инверторы типа 74HC14, доступные на плате стенда.

Рис. 16. Реализация функции ИЛИ на ЛЭ 2И-НЕ (а) и И на ЛЭ типа 2ИЛИ-НЕ (б)

7. Соберите схему одноразрядного сумматора согласно Рис. 17. Обратите внимание, что данная схема отличается от рассмотренной в описании лабораторной работы, так как на плате стенда присутствуют только универсальные ЛЭ И-НЕ, ИЛИ-НЕ:

Рис. 17. Схема для исследования одноразрядного сумматора

Учтите, что в схеме присутствуют логические элементы типа ИСКЛЮЧАЮЩЕЕ ИЛИ. Найдите на плате стенда такие ЛЭ, используя уже выполненные пункты задания.

8. Устанавливая на переключателях значения входных сигналов схемы, вычислите при помощи сумматора значения выражений, указанных в таблице, и заполните ее:

Таблица 2.

| Выражение | Результат (двоичное число) | Результат (десятичное число) |

|-----------|----------------------------|------------------------------|

| 0+0+0     |                            |                              |

| 0+0+1     |                            |                              |

| 0+1+0     |                            |                              |

| 0+1+1     |                            |                              |

| 1+0+0     |                            |                              |

| 1+0+1     |                            |                              |

| 1+1+0     |                            |                              |

| 1+1+1     |                            |                              |

Обратите внимание, что вход переноса одноразрядного сумматора фактически эквивалентен любому из входов слагаемых.

9. Соберите схему дешифратора «2 в 4» на ЛЭ согласно схеме Рис. 18 и заполните таблицу истинности для этой схемы (4 строки).

Рис. 18. Схема для исследования дешифратора «2 в 4»

В качестве инверторов используйте имеющиеся в плате стенда элементы 74HC14 (инвертирующие триггеры Шмитта).

## 2. МУЛЬТИВИБРАТОРЫ НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

### 2.1. Краткое описание лабораторной работы

1. В лабораторной работе изучаются наиболее популярные схемы мультивибраторов на ЛЭ 74HC14, 74HC00, 74HC02.

2. Одновременно собирается три схемы: две на звуковую частоту и одна – на частоту в доли или единицы Гц.

3. Для исследования собранных схем используется цифровой осциллограф.

4. На основе собранных схем собирается и отлаживается более сложная схема двухтонального генератора звука.

### 2.2. Основные теоретические сведения

Самой простой схемой мультивибратора на логических элементах является схема, которую можно построить на инвертирующем триггере Шмитта. По логике работы она очень похожа на схему мультивибратора на аналоговом компараторе с гистерезисом, которая подробно описана в [АнCXT].

Обычный элемент НЕ (инвертор) логически похож на инвертирующий аналоговый компаратор без гистерезиса, опорным напряжением для которого является пороговое напряжение ЛЭ  $U_{\text{ПОР}}$ : если входное напряжение ниже порогового, оно воспринимается как уровень лог. «0» и на выходе формируется напряжение лог. «1», и наоборот.

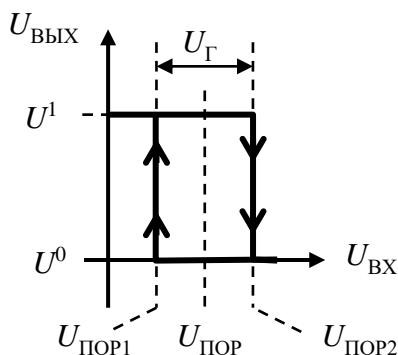

Среди стандартных микросхем практически любой серии, однако, встречаются несколько необычные элементы, входные каскады которых имеют гистерезис, т.е. являются триггерами Шмитта. Для таких элементов, рассматривая пример инвертора, переход из лог. «0» в лог. «1» по выходу происходит при меньшем уровне входного напряжения  $U_{\text{ПОР}1}$ , чем обратный переход при  $U_{\text{ВХ}} = U_{\text{ПОР}2}$ . Разница входных напряжений, при которых происходит изменение выходного логического уровня, т.е.  $U_{\Gamma} = (U_{\text{ПОР}2} - U_{\text{ПОР}1})$ , является шириной петли гистерезиса триггера Шмитта (см. Рис. 19).

Рис. 19. Гистерезис инвертирующего триггера Шмитта

Если в аналоговой схеме сравнения напряжений ширину петли гистерезиса можно программировать при помощи резисторов в обвязке компаратора или ОУ, то для ЛЭ с триггером Шмитта величины  $U_{\text{ПОР}1,2}$  являются паспортными, и никаких резисторов, естественно, не требуется. Согласно документации, для интегральной микросхемы 74HC14 при напряжении питания 4.5 В величина  $U_{\text{ПОР}2}$ , так же называемая верхним порогом переключения (англ. «positive going threshold») составляет порядка 2.4 В, а величина нижнего порога  $U_{\text{ПОР}1}$  (англ. «negative going threshold») — порядка 1.4 В.

Основная задача, решаемая при помощи инвертирующих триггеров Шмитта 74HC14 и их аналогов — обеспечение помехозащищенности входов цифровых схем и узлов, а вовсе не сравнение напряжений, в связи с чем точность, с которой выдерживаются величины  $U_{\text{ПОР}1,2}$ , невелика. Так, при питании 4.5 В ширина петли гистерезиса 74HC14 может изменяться от 0.4 до порядка 1.4 В. В связи с этим расчеты частоты мультивибратора, построенного на таком элементе, дают лишь оценочный результат, что, впрочем, не является проблемой при создании

таких радиолюбительских схем, как генераторы звуковых сигналов, гирлянды, мигающие индикаторы и т.д.

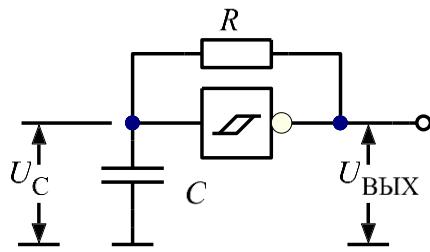

Схема мультивибратора на инвертирующем триггере Шмитта показана на Рис. 20.

Рис. 20. Мультивибратор на инвертирующем триггере Шмитта

После включения питания конденсатор  $C$  разряжен, и на вход ЛЭ поступает напряжение ниже величины  $U_{\text{пор1}}$ . Это означает, что на выходе формируется напряжение лог. «1», для ЛЭ серии 74HC равное  $U_{\text{вых}} = U^1 \approx U_{\Pi}$ , и начинается заряд конденсатора током, протекающим через резистор  $R$  из выхода ЛЭ. Когда напряжение на его верхней обкладке достигает уровня  $U_{\text{пор2}}$ , выходное напряжение схемы скачкообразно изменяется на  $U_{\text{вых}} = U^0 \approx 0$  В, и начинается разряд конденсатора током, протекающим через резистор  $R$ , но уже в выход ЛЭ. Таким образом, возникает устойчивая генерация прямоугольных импульсов на выходе схемы.

Для стабильной работы схемы номинал резистора должен быть не слишком большим. Входной ток утечки ЛЭ 74HC14 составляет порядка 100 нА. Если сопротивление  $R$  не превышает 1 МОм, тогда величина тока, перезаряжающего конденсатор в диапазоне напряжений от  $U_{\text{пор1}}$  до  $U_{\text{пор2}}$ , окажется на порядок больше входного тока утечки ЛЭ, и в расчетах им можно будет пренебречь.

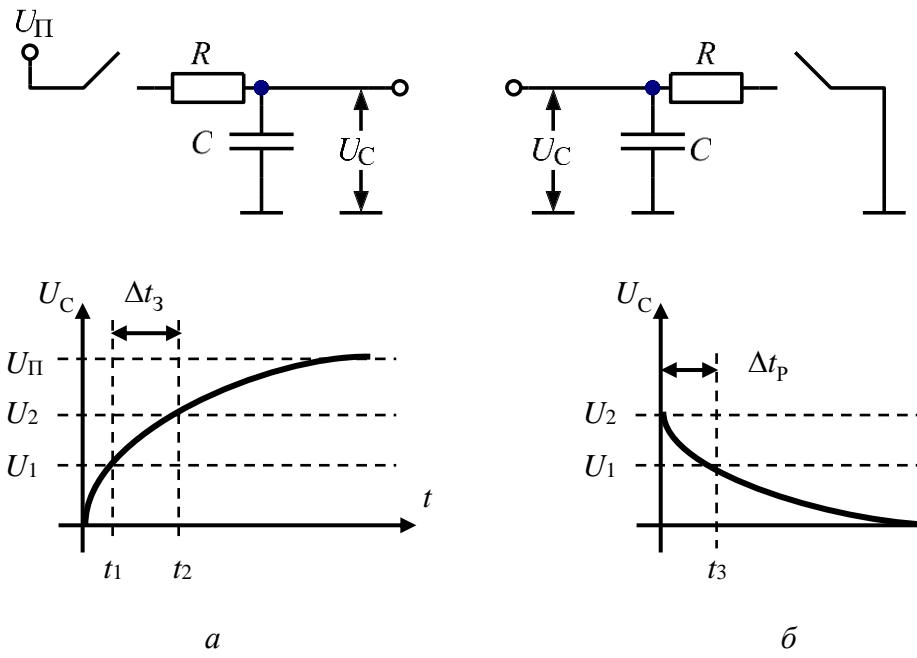

В [АнСХТ] было показано, что при подаче в нулевой момент времени на интегрирующую RC-цепь прямоугольного импульса амплитудой  $U_{\Pi}$  напряжение на обкладках конденсатора будет меняться по экспоненциальному закону вида

$$(2) \quad U_C(t) = U_{\Pi} \left( 1 - e^{-t/\tau} \right), \text{ где } \tau = RC.$$

Процесс заряда конденсатора при этом описывается кривой, показанной на Рис. 21, а.

Рис. 21. Процесс заряда (а) и разряда (б) конденсатора в интегрирующей RC-цепи

Для математического анализа работы мультивибратора, используя соотношение (2), выведем формулу, которая позволяет рассчитать время  $\Delta t_3$ , необходимое, чтобы зарядить конденсатор, включенный в интегрирующую RC-цепь, от некоторого напряжения  $U_1$  до  $U_2$  источником, выдающий напряжение  $U_{\Pi}$ . До напряжения  $U_1$  конденсатор зарядится за время  $t_1$ , которое можно определить из соотношения  $U_1 = U_{\Pi} \left(1 - e^{-t_1/\tau}\right)$ . Очевидно,  $t_1 = -\tau \cdot \ln \left(1 - \frac{U_1}{U_{\Pi}}\right)$ . Далее конденсатор продолжит заряд до уровня напряжения  $U_2$ . На заряд конденсатора с нуля до этого напряжения уйдет время  $t_2$  равное, соответственно,  $t_2 = -\tau \cdot \ln \left(1 - \frac{U_2}{U_{\Pi}}\right)$ . Искомое время  $\Delta t_3$  составит разницу этих двух времен, то есть,

$$(3) \Delta t_3 = t_2 - t_1 = -\tau \cdot \ln \left( \frac{1 - \frac{U_2}{U_{\Pi}}}{1 - \frac{U_1}{U_{\Pi}}} \right) = -RC \cdot \ln \left( \frac{U_{\Pi} - U_2}{U_{\Pi} - U_1} \right).$$

По аналогии с выражением (2) можно составить соотношение, описывающее процесс разряда конденсатора, изначально заряженного до напряжения  $U_2$  через резистор, если в нулевой момент времени замыкается ключ и резистор оказывается подключен к земле:

$$(4) U_C(t) = U_2 \cdot e^{-t/\tau}, \text{ где } \tau = RC.$$

Время разряда конденсатора, через которое напряжение на конденсаторе опустится до уровня  $U_1$ , очевидно, составит

$$(5) t_P = t_3 = -\tau \cdot \ln \left( \frac{U_1}{U_2} \right).$$

Соотношения (3) и (5) позволяют легко вывести формулы для расчета длительности импульса и паузы сигнала на выходе любого мультивибратора.

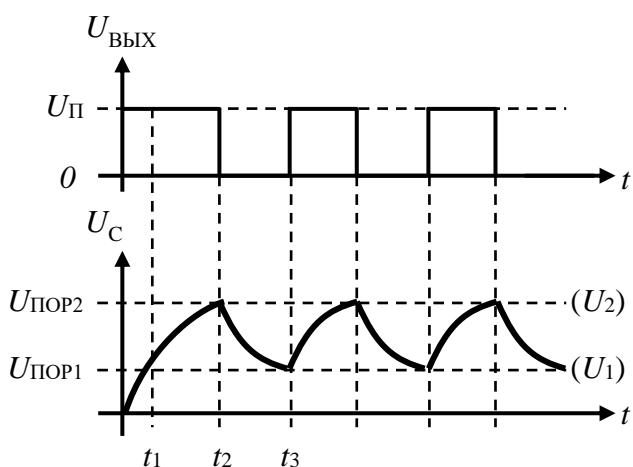

В случае мультивибратора на инвертирующем триггере Шмитта, напряжение на конденсаторе изменяется между величинами его пороговых напряжений по экспоненциальному закону и временные диаграммы напряжений на конденсаторе и выходе схемы имеют вид, показанный на Рис. 22.

Рис. 22. Осциллограммы напряжений в узлах схемы мультивибратора на инвертирующем триггере Шмитта

Примем, что напряжение лог. «1» на выходе ЛЭ, изготовленного по КМОП-технологии, при малом выходном токе составляет  $U^1 = U_{\Pi}$ , а напряжение лог. «0»  $U^0 = 0$ . Тогда длительность импульса на выходе схемы составляет, согласно (3),

$$(6) t_I = -RC \cdot \ln \left( \frac{U_{\Pi} - U_{\text{ПОР}2}}{U_{\Pi} - U_{\text{ПОР}1}} \right),$$

а паузы, в соответствии с (5),

$$(7) t_{\Pi} = -RC \cdot \ln \left( \frac{U_{\text{ПОР}1}}{U_{\text{ПОР}2}} \right).$$

С учетом свойств логарифмов период колебаний на выходе схемы можно рассчитать, как

$$(8) T = t_{\text{И}} + t_{\Pi} = -RC \cdot \ln \left( \frac{U_{\Pi} - U_{\text{ПОР2}}}{U_{\Pi} - U_{\text{ПОР1}}} \cdot \frac{U_{\text{ПОР1}}}{U_{\text{ПОР2}}} \right) = \frac{1}{f}$$

где  $f$  – рабочая частота мультивибратора.

Если подставить в выражение (8) типичные значения порогов переключения микросхемы 74HC14 для напряжения питания 5 В, можно получить простое выражение для оценки периода выходных сигналов вида:

$$(9) T = -RC \cdot \ln \left( \frac{5-2.38}{5-1.4} \cdot \frac{1.4}{2.38} \right) \approx 0.8RC$$

Использовать для оценки периода выходного сигнала безразмерный коэффициент с более высокой точностью, чем 0.8, не принято: с учетом большого разброса пороговых напряжений триггера Шмитта и невысокой точности популярных керамических и электролитических конденсаторов, расчет носит весьма приблизительный характер. Это, впрочем, не является проблемой для области применения схемы.

Особое внимание следует уделить тому обстоятельству, что формула для оценки выходной частоты сильно зависит от конкретного семейства микросхем. Так, для ЛЭ типа 74HCT14 пороговые напряжения заметно отличаются от таковых для 74HC14, и безразмерный коэффициент в выражении (9) составит уже 0.67. Очевидно, асимметрия переходной характеристики триггера Шмитта (см. Рис. 19) приводит к тому, что коэффициент заполнения выходного сигнала не равен 50%, хоть и близок к этой величине.

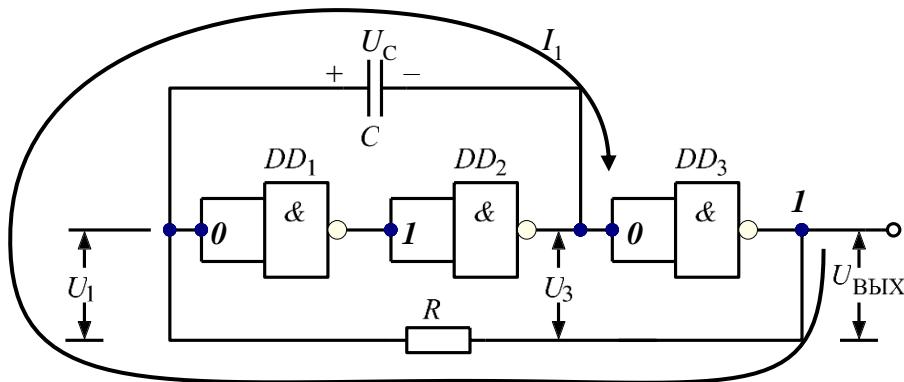

Другая крайне популярная схема мультивибратора на ЛЭ строится с использованием инверторов без гистерезиса, или, чаще, с использованием наиболее распространенных универсальных ЛЭ, работающих в роли инверторов. Данная схема (см. Рис. 23), несмотря на чуть большую сложность, по историческим причинам является более популярной, чем предыдущая. Это связано с некогда крайне высокой распространенностью инверторов и универсальных ЛЭ, тогда как инвертирующие триггеры Шмитта на заре развития отечественной цифровой схемотехники были не столь доступны радиолюбителям.

Рис. 23. Мультивибратор на инверторах, исходное состояние

Прямых аналогий между этой схемой и хорошо известными схемами мультивибраторов на ОУ и транзисторах нет.

При отсутствии конденсатора и закороченном резисторе схема вырождается в три последовательно включенных инвертора, причем выход последнего подключен ко входу первого. Такая схема по определению нестабильна, т.к. выполняет функцию  $X = \bar{X}$ . Без пассивных компонентов на выходе схемы возникли бы импульсы, частота которых была бы ограничена лишь быстродействием ЛЭ и составляла бы для серии микросхем 74HC многие мегагерцы.

Наличие резистора и конденсатора вносит прогнозируемые задержки между переключениями выходного ЛЭ схемы. Предположим, что после включения питания схемы первый ЛЭ  $DD_1$  находится в состоянии  $U_1 = U^0$  (лог. «0») по входу. Тогда напряжение на выходе  $DD_2$  ( $U_3$ ) также будет равно уровню лог. «0», а  $U_{\text{вых}} = U^1 \approx 5$  В.

Т.к.  $U_3$  соответствует уровню лог. «0» ( $\approx 0$  В), а конденсатор не может перезарядиться мгновенно, в течение некоторого времени будет справедливым неравенство  $U_1 < U_{\text{ПОР}}$ , т.е.  $U_1$  будет восприниматься ЛЭ  $DD_1$  как лог. «0». В течение всего этого времени через схему будет протекать ток  $I_1$ , который будет заряжать конденсатор  $C$  до некоторого растущего во времени напряжения  $U_C$ , в полярности, указанной на Рис. 23. Правая обкладка конденсатора в этот интервал времени подключена к «земле» через выход ЛЭ.

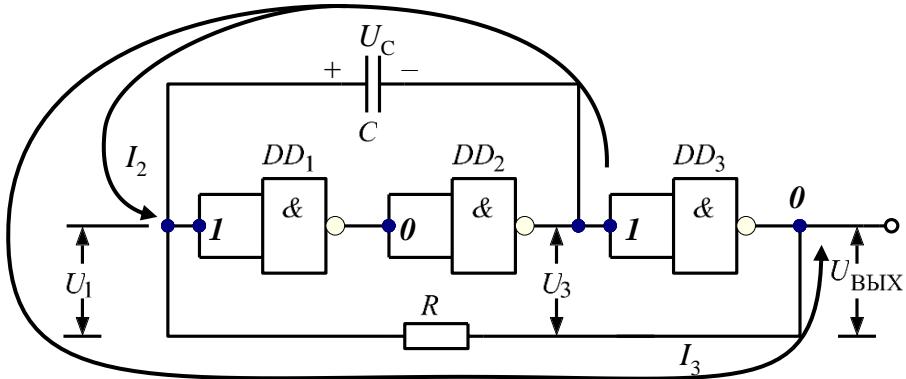

Когда  $U_C$  и, соответственно, напряжение  $U_1$  достигнет уровня  $U_{\text{ПОР}}$  ( $\approx 2.5$  В для серии ЛЭ 74HC), все ЛЭ схемы изменят состояние на противоположное (см. Рис. 24).  $U_3$  становится равным  $U^1 \approx U_{\text{П}} = 5$  В. Это напряжение ( $U_3$ ) складывается с напряжением, до которого зарядился конденсатор, и прикладывается ко входу ЛЭ  $DD_1$ .

Рис. 24. Мультивибратор на инверторах, состояние после первого переключения

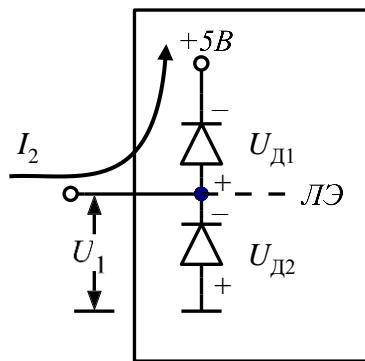

Теоретически, сразу после переключения  $U_1$  составило бы  $U_1 = U_3 + U_C = 7.5$  В. На практике же, напряжения на входах ЛЭ ограничены встроенными защитными диодами,ключенными согласно Рис. 25.

Рис. 25. Защитные диоды на входах цифровых микросхем

в режиме ограничения входного напряжения

При эксплуатации ЛЭ в штатном режиме, когда его входное напряжение не превышает напряжения питания, влияние этих диодов практически отсутствует, и входные токи ЛЭ, выполненного по КМОП-технологии, составляют всего порядка 100 нА. Однако сразу после переключения верхний диод оказывается смещенным в прямом направлении, и пропускает через себя значительный ток  $I_2$ , втекающий в цепь питания схемы. Ток  $I_2$  ограничен лишь нагрузочной способностью ЛЭ  $DD_2$  и составляет для серии 74HC порядка 20-25 мА. Этот ток быстро разряжает конденсатор до уровня  $U_C$  порядка  $U_{\text{д}1}$ , после чего значительно уменьшается. Далее за разряд конденсатора отвечает лишь ток  $I_3$ , который должен быть меньше максимального выходного тока ЛЭ, и составляет не более 10-15 мА. В процессе разряда конденсатора напряжение  $U_1$  до величины порога переключения ЛЭ  $U_{\text{ПОР}} \approx U_{\text{П}} / 2 = 2.5$  В.

Далее опять происходит переключение схемы и логические уровни в ее узлах оказываются аналогичными показанному на Рис. 23. Однако, полярность напряжения на обкладках

конденсатора оказывается противоположной показанному на Рис. 24. В дело вступает нижний защитный диод (см. Рис. 25), быстро разряжая конденсатор так, что  $U_1$  оказывается равным приблизительно  $-U_{D2}$ . После этого ток через нижний защитный диод значительно падает, и происходит сравнительно медленная перезарядка конденсатора, скорость которой в схеме задается резистором, до момента времени, когда опять выполняется условие  $U_1 = U_{\text{ПОР}}$ . Далее схема переходит в состояние согласно Рис. 24 и т.д. В схеме возникает устойчивая генерация.

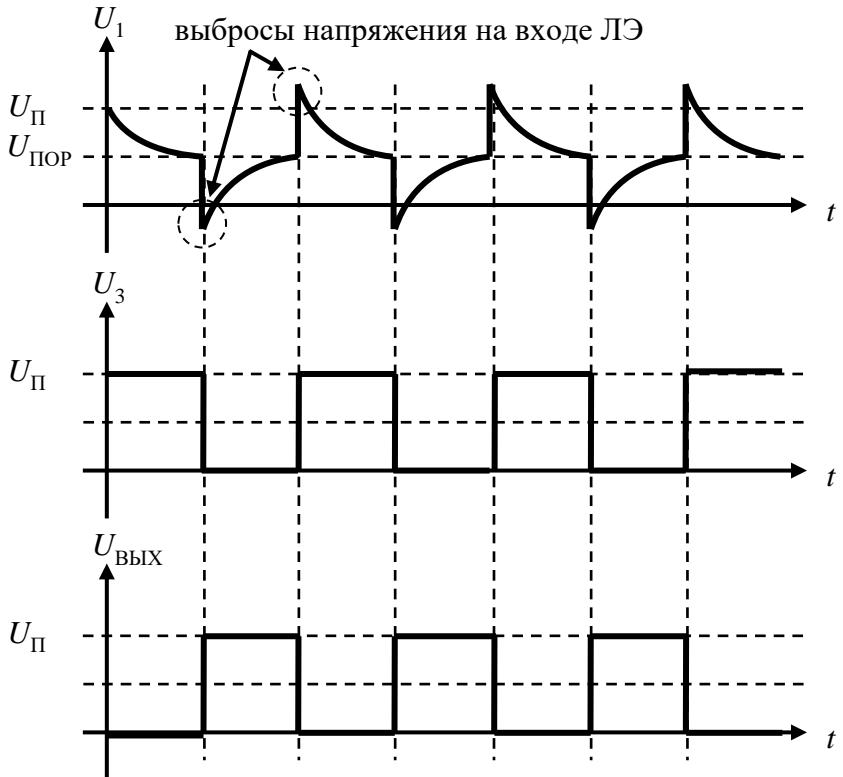

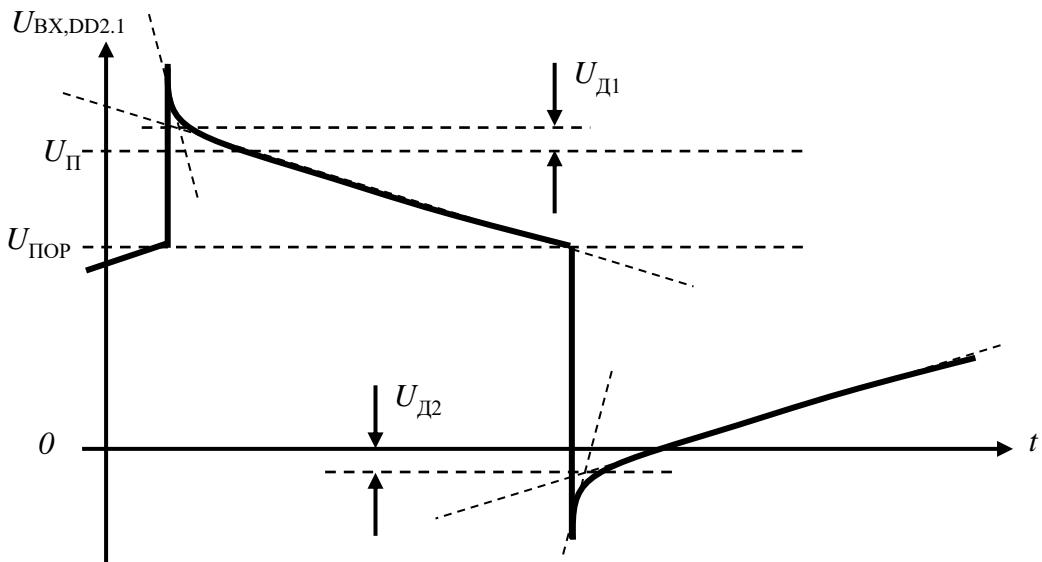

Временные диаграммы напряжений схемы Рис. 23 показаны ниже. В соответствии с принципом работы схемы, на входе ЛЭ  $DD_1$  имеют место непродолжительные положительные и отрицательные выбросы напряжения, блокируемые защитными диодами.

Рис. 26. Временные диаграммы напряжений в узлах схемы мультивибратора на инверторах

Для того чтобы оценить длительность импульса напряжения на выходе схемы, вновь воспользуемся формулой (3), по которой рассчитывается время зарядки конденсатора от некоторого начального  $U_1$  до некоторого конечного значения напряжения  $U_2$  от источника  $U_{\text{П}}$ . В эту формулу в качестве  $U_1$  подставим величину  $(-U_{D2})$ , а в качестве конечного  $U_2$  – величину порогового напряжения ЛЭ  $U_{\text{ПОР}}$ . Тогда

$$(10) \quad t_i = -RC \cdot \ln \left( \frac{U_{\text{П}} - U_{\text{ПОР}}}{U_{\text{П}} + U_{D2}} \right)$$

Аналогично используем для оценки длительности паузы, когда конденсатор разряжается от напряжения ( $U^1 \approx U_{\text{П}} + U_{D1}$ ) до напряжения переключения ЛЭ  $U_{\text{ПОР}}$ , выражение (5):

$$(11) \quad t_{\Pi} = -RC \cdot \ln \left( \frac{U_{\text{ПОР}}}{U_{\text{П}} + U_{D1}} \right).$$

В литературе зачастую считают, что порог переключения ЛЭ серии НС составляет  $0.5 \cdot U_{\text{П}}$ , а падением напряжения на защитных диодах пренебрегают, считая их нулевыми. В этом случае формула для оценки периода колебаний на выходе схемы предельно упрощается:

$$T = t_i + t_{\Pi} = -RC \cdot \ln(0.5 \cdot 0.5) \approx 1.4 \cdot RC.$$

Важно понимать, что данное выражение, хоть и весьма удобно, получено при помощи весьма грубых приближений и дает очень приблизительный результат.

Полезной особенностью мультивибратора на инверторах, сконструированных из универсальных ЛЭ, в частности, типа 2И-НЕ, является крайняя легкость создания цифрового входа разрешения работы схемы. Если отключить от точки приложения напряжения  $U_1$  один из входов  $DD_1$  (см. Рис. 23), и подать на него уровень лог. «0», то на выходе схемы будет удерживаться постоянный уровень лог. «1». Если же на этот вход подать уровень лог. «1», начнется работа мультивибратора. Таким образом, полученный вход является входом разрешения с высоким активным уровнем.

Коэффициент заполнения выходного сигнала такой схемы, построенной на микросхемах семейства 74HC, как и для схемы мультивибратора на инвертирующем триггере Шmittта, близок к 50%. Асимметрия выходного сигнала здесь определяется как отличием порогового напряжения ЛЭ от величины  $0.5 \cdot U_{\text{П}}$ , так и отличием вольтамперных характеристик защитных диодов на входах элемента  $DD_1$ .

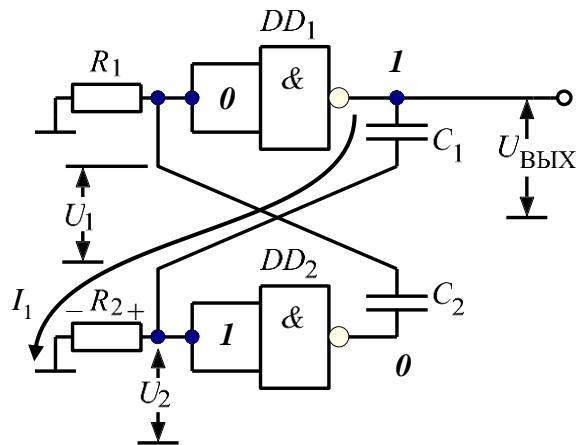

Обе описанные схемы содержат всего одну времязадающую RC-цепь и не позволяют индивидуально задать длительность импульса и длительность паузы на выходе. Этого недостатка лишена еще одна распространенная схема мультивибратора на ЛЭ, показанная на Рис. 27, выгодно отличающаяся от прочих схем с двумя RC-цепями минимальным числом компонентов. Идеологически эта схема очень похожа на мультивибратор на транзисторах (см. [АнСХТ]).

Рассмотрим состояние схемы сразу после включения ее питания. Оба конденсатора,  $C_1$  и  $C_2$ , разряжены. Оба входа ЛЭ подтянуты резисторами  $R_{1,2}$  к земле, т.е. на обоих выходах ЛЭ должен сформироваться уровень лог. «1». Как только на выходе первого из двух ЛЭ возникнет этот уровень лог. «1», напряжение  $U^1$  через конденсатор, который не может перезарядиться мгновенно, поступит на вход второго ЛЭ, и на его выходе возникнет уже уровень лог. «0». Поскольку ЛЭ не идентичны, их быстродействие различается, и один ЛЭ после включения питания «опередит» второй, сформировав лог. «1» на выходе. После подачи питания они, таким образом, перейдут в разные состояния.

Рис. 27. Мультивибратор на ЛЭ с индивидуальной установкой времен импульса и паузы, исходное состояние

Пусть, для определенности, после подачи питания схема быстро переходит в состояние, показанное на Рис. 27 с уровнем лог. «1» на выходе, где действует напряжение  $U_{\text{вых}}$ . Схема останется в этом состоянии, пока на входе  $DD_2$  действует уровень лог. «1», т.е. пока через  $R_2$  протекает ток  $I_1$ , заряжающий  $C_1$ , а напряжение, до которого зарядился  $C_1$ , не превышает величины ( $U_{\text{П}} - U_{\text{пор}}$ ).

В соответствии с выражением (3) можно получить формулу, которая определяет длительность импульса на выходе схемы. Для этого подставим в качестве конечного напряжения, до которого заряжается конденсатор, величину ( $U_{\text{П}} - U_{\text{пор}}$ ). В качестве начального напряжения, от которого заряжается конденсатор, подставим нулевое значение. Это корректно и для

рассмотрения момента подачи питания схемы, и для анализа ее работы в устоявшемся режиме, в чем мы еще убедимся ниже:

$$(12) \quad t_{ii} = -R_2 C_1 \cdot \ln \left( \frac{U_{\Pi} - (U_{\Pi} - U_{\text{ПОР}})}{U_{\Pi}} \right) = -R_2 C_1 \cdot \ln \left( \frac{U_{\text{ПОР}}}{U_{\Pi}} \right)$$

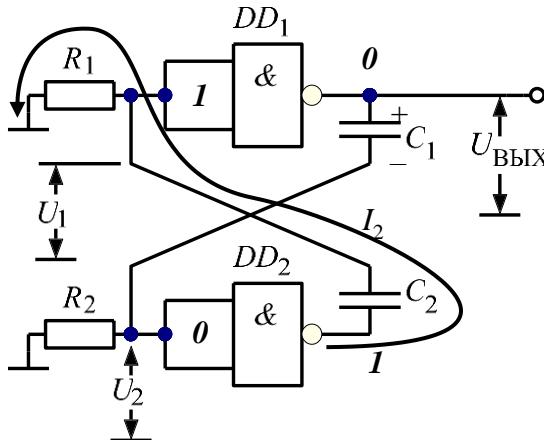

Когда напряжение, до которого зарядился конденсатор, достигает величины  $(U_{\Pi} - U_{\text{ПОР}})$ , в соответствии с правилом Кирхгофа для контура величина  $U_2$  на входе  $DD_2$  падает до уровня порогового напряжения  $U_{\text{ПОР}}$  и схема меняет свое состояние на противоположное: ЛЭ  $DD_2$  определит состояние своего входа как лог. «0» и перейдет в лог. «1» по выходу.

Этот уровень напряжения приложится через разряженный конденсатор  $C_2$  ко входу  $DD_1$ , и он тоже изменит свое состояние на противоположное ( $U_{\text{ВЫХ}} = U^0$ ), показанное на Рис. 28. Как и для предыдущей схемы, при этом на вход  $DD_2$  поступит отрицательное напряжение, до которого зарядился конденсатор  $C_1$ . Оно равно  $(U_{\Pi} - U_{\text{ПОР}})$  и блокируется нижним защитным диодом ЛЭ. Благодаря ему конденсатор  $C_1$  быстро разрядится до напряжения  $U_{d2}$ , затем скорость разряда снизится и будет определяться особенностями вольтамперной характеристики защитного диода. Для простоты анализа будем считать, что за время паузы  $C_1$  разряжается до нуля.

Во время паузы конденсатор  $C_2$  заряжается током  $I_2$ , протекающим из выхода  $DD_2$  и резистор  $R_1$  в землю. Состояние схемы вернется к исходному, как только  $C_2$  зарядится до уровня напряжения  $(U_{\Pi} - U_{\text{ПОР}})$ . Аналогично выражению (12), длительность паузы можно определить как

$$(13) \quad t_{ii} = -R_1 C_2 \cdot \ln \left( \frac{U_{\text{ПОР}}}{U_{\Pi}} \right).$$

Рис. 28. Мультивибратор на ЛЭ с индивидуальной установкой времен импульса и паузы, состояние после первого переключения

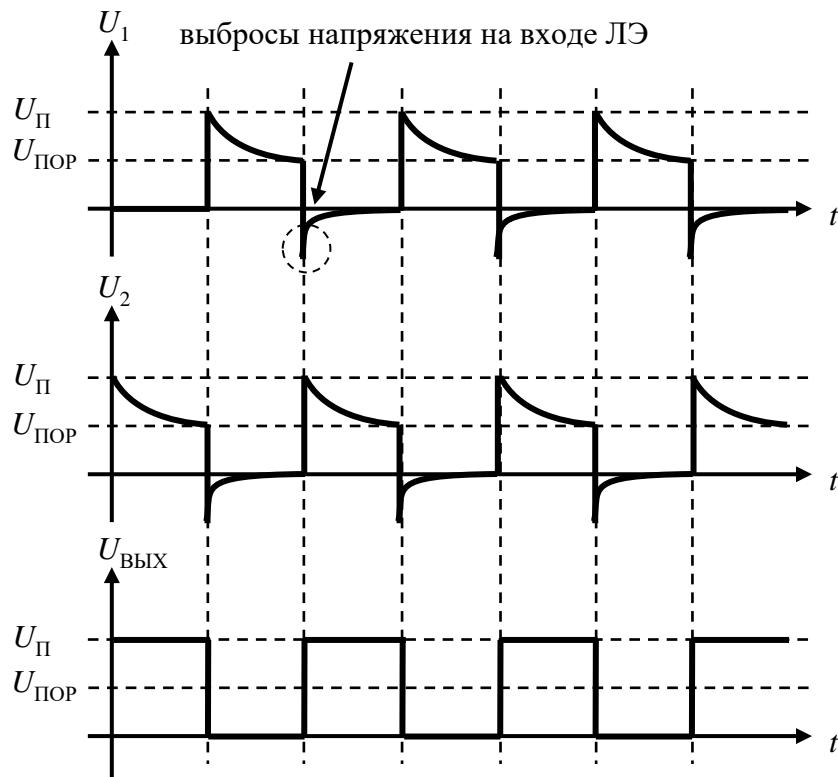

Период следования прямоугольных импульсов на выходе можно определить при помощи выражения:

$$(14) \quad T = t_{ii} + t_{ii} = -\ln \left( \frac{U_{\text{ПОР}}}{U_{\Pi}} \right) \cdot [R_2 C_1 + R_1 C_2].$$

Как видно, в первом приближении наличие защитных диодов на поведение схемы не влияет. В отличие от предыдущей схемы, здесь имеют место лишь небольшие отрицательные выбросы напряжения на входе ЛЭ

Рис. 29. Временные диаграммы напряжений схемы мультивибратора на ЛЭ с независимой установкой длительности импульса и паузы

В действительности к концу каждого интервала времени, когда схема пребывает в одном из двух устойчивых состояний, конденсатор на входе того ЛЭ, который в данный момент выдает уровень лог. «1», разряжается не до конца. Степень его остаточного заряда определяется и номиналом резистора времязадающей цепи, куда он включен, и вольтамперной характеристикой нижнего защитного диода ЛЭ, и постоянной времени второй времязадающей цепи (она влияет на продолжительность разряда этого конденсатора). В результате, когда один ЛЭ, переходит по выходу из состояния лог. «0» в лог. «1», ко входу другого ЛЭ сразу после этого прикладывается не напряжение  $U_1 \approx U_{\text{П}}$ , а несколько меньшее. Это приводит к тому, что длительности импульса и паузы на выходе схемы оказываются несколько ниже расчетных. Математическое описание этого эффекта – и крайне трудоемкая задача, и бессмысленная, т.к. мультивибраторы на времязадающих RC-цепях по определению являются неточными устройствами. Там, где требуются источники стабильной частоты, применяются сложные синтезаторы частот, в основе которых лежат генераторы, включающие в свой состав прецизионный кварцевый резонатор.

Многообразие схем мультивибраторов на цифровых микросхемах описанными решениями, естественно, не исчерпывается. Однако большинство таких схем можно анализировать, используя описанный в данной главе подход.

## 2.3. Задание на проведение исследований

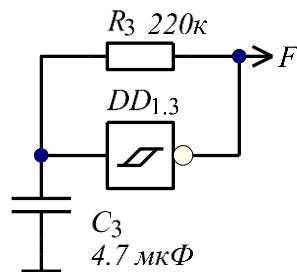

1. Соберите схему №1: мультивибратор на инвертирующем триггере Шмитта (см. Рис. 30), используя для времязадающей цепи компоненты, согласно номеру бригады, по таблице. Перед сборкой схемы измерьте при помощи мультиметра реальное значение емкости конденсатора времязадающей цепи. В дальнейшем во всех теоретических расчетах используйте измеренные (а не написанные на плате стенда) значения емкостей.

Обратите внимание, что токоограничительный резистор уже включен последовательно светодиоду на плате, и для использования светодиода достаточно правильно поставить перемычку.

Таблица 3.

| №<br>бри-<br>гады | Номиналы компонентов для схем мультивибраторов |            |             |            |             |            |             |            |

|-------------------|------------------------------------------------|------------|-------------|------------|-------------|------------|-------------|------------|

|                   | Схема №1                                       |            | Схема №2    |            | Схема №3    |            |             |            |

|                   | $R_1$ , кОм                                    | $C_1$ , нФ | $R_2$ , кОм | $C_2$ , нФ | $R_3$ , кОм | $C_3$ , нФ | $R_4$ , кОм | $C_4$ , нФ |

| 1                 | 220                                            | 1000       | 47          | 10         | 10          | 220        | 2.2         | 100        |

| 2                 | 220                                            | 470        | 47          | 10         | 2.2         | 1          | 470         | 47         |

| 3                 | 100                                            | 1000       | 220         | 1          | 10          | 100        | 1           | 10         |

| 4                 | 220                                            | 4700       | 47          | 47         | 10          | 1          | 470         | 10         |

| 5                 | 100                                            | 4700       | 220         | 1          | 47          | 220        | 2.2         | 10         |

| 6                 | 220                                            | 1000       | 100         | 1          | 10          | 10         | 47          | 47         |

| 7                 | 470                                            | 470        | 47          | 10         | 1           | 100        | 2.2         | 220        |

| 8                 | 220                                            | 4700       | 100         | 47         | 47          | 220        | 4.7         | 100        |

| 9                 | 100                                            | 4700       | 220         | 10         | 10          | 47         | 47          | 100        |

| 10                | 220                                            | 1000       | 100         | 10         | 47          | 100        | 10          | 47         |

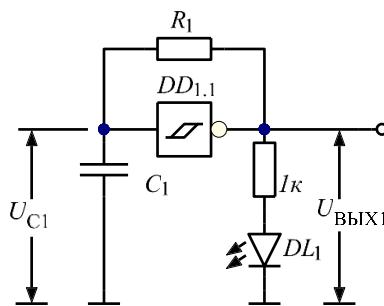

Рис. 30. Схема №1 для исследования мультивибратора на инвертирующем триггером Шмитта

2. Подключите канал №1 осциллографа к выходу схемы  $U_{\text{вых}1}$ , канал №2 – к верхней обкладке конденсатора  $C_1$  ( $U_{C1}$ ). Измерьте при помощи осциллографа и запишите в протокол наблюдений:

- Длительность импульса  $t_{\text{и1}}$ .

- Длительность паузы  $t_{\text{п1}}$ .

- Пороговые напряжения инвертера с триггером Шмитта  $U_{\text{ПОР1}}$  и  $U_{\text{ПОР2}}$ . При достижении одного из двух пороговых значений напряжением  $U_{C1}$  состояние выхода ЛЭ меняется на противоположное (при этом также меняется направление тока конденсатора – заряд/разряд).

При составлении отчета сравните измеренные значения длительностей импульса и паузы со значениями, рассчитанными по соотношениям (6) и (7). Напряжение питания микросхем платы составляет 5 В. При расчете используйте измеренные значение емкости конденсатора и пороговые напряжения ЛЭ.

3. Зарисуйте или сфотографируйте осциллограмму, на которой одновременно присутствуют сигналы каналов №1 и №2. Приложите осциллограмму к отчету по лабораторной работе.

4. Не разбирайте схемы №1, соберите схему №2: простейший мультивибратор на ЛЭ типа 2И-НЕ (см. Рис. 31). Выберите номиналы компонентов времязадающей цепи согласно номеру бригады (Таблица 3). Перед сборкой схемы измерьте при помощи мультиметра реальное значение емкости конденсатора времязадающей цепи.

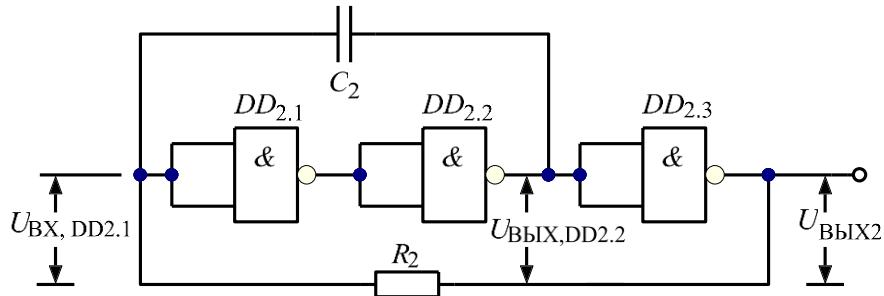

Рис. 31. Схема №2 для исследования простейшего мультивибратора на ЛЭ типа 2И-НЕ

5. Подключите канал №1 осциллографа к выходу всей схемы  $U_{\text{вых}2}$ , канал №2 – ко входу ЛЭ  $DD_{2.1}$  ( $U_{\text{вх},DD2.1}$ ), канал №3 – к выходу  $DD_{2.2}$  ( $U_{\text{вых},DD2.2}$ ). Измерьте при помощи осциллографа и запишите в протокол наблюдений:

- Длительность импульса  $t_{12}$ .

- Длительность паузы  $t_{12}$ .

- Пороговое напряжение ЛЭ  $U_{\text{пор}}$ . Когда  $U_{\text{вх},DD2.1}$  достигает порогового значения, схема меняет состояние на противоположное, а само входное напряжение  $DD_{2.1}$  меняется скачкообразно.

- Напряжения отпирания верхнего защитного диода ЛЭ  $U_{D1}$ . Для его определения проще всего использовать курсоры осциллографа. Напряжением отпирания диода считайте разность напряжения на входе  $DD_{2.1}$ , при котором начинается медленный разряд конденсатора  $C_2$  по экспоненциальному закону (т.е. прекращается быстрый разряд через диод) и напряжения питания (см. Рис. 32).

- Напряжения отпирания нижнего защитного диода ЛЭ  $U_{D2}$ . Напряжением отпирания диода считайте значение напряжения на входе  $DD_{2.1}$ , при котором начинается медленный заряд конденсатора  $C_2$  по экспоненциальному закону (см. Рис. 32).

Рис. 32. К определению напряжения отпирания защитных диодов

При составлении отчета сравните полученные значения длительности импульса и паузы с величинами, рассчитанными по соотношениям (10) и (11). При расчете используйте измеренные

значения емкости конденсатора, а также пороговое напряжение и напряжения отпирания защитных диодов.

6. Зарисуйте или сфотографируйте осциллограмму, на которой одновременно присутствуют сигналы каналов №1, №2 и №3. Приложите осциллограмму к отчету по лабораторной работе.

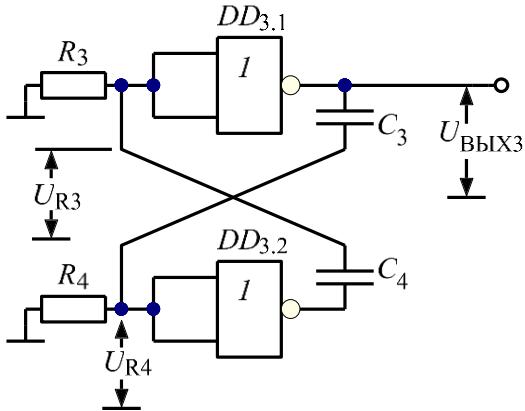

7. Не разбирая схем №1 и №2, соберите схему №3: мультивибратор на ЛЭ типа 2ИЛИ-НЕ с регулируемым коэффициентом заполнения (см. Рис. 33). Выберите номиналы компонентов времязадающей цепи согласно номеру бригады (Таблица 3). Перед сборкой схемы измерьте при помощи мультиметра реальные значения емкостей конденсаторов времязадающих цепей.

Рис. 33. Схема №3 для исследования мультивибратора на ЛЭ типа 2ИЛИ-НЕ с регулируемым коэффициентом заполнения

8. Подключите канал №1 осциллографа – к выходу всей схемы  $U_{\text{вых}3}$ , канал №2 – ко входу ЛЭ  $DD_{3.1}$  ( $U_{R3}$ ), канал №3 – ко входу  $DD_{3.2}$  ( $U_{R4}$ ). При помощи осциллографа измерьте и запишите в протокол наблюдений:

- Длительности импульса  $t_{\text{из}}$ .

- Длительность паузы  $t_{\text{пз}}$ .

- Пороговое напряжение ЛЭ  $U_{\text{пор}}$ . Когда напряжение  $U_{R3}$  достигает порогового значения, состояние схемы меняется на противоположное, а само напряжение  $U_{R3}$  меняется скачкообразно.

При составлении отчета сравните полученные значения с рассчитанными по соотношениям (12) и (13). При расчете используйте измеренные значения емкостей конденсаторов, а также пороговое напряжение ЛЭ.

9. Зарисуйте или сфотографируйте осциллограмму, на которой одновременно присутствуют сигналы каналов №1, №2 и №3. Приложите осциллограмму к отчету по лабораторной работе.

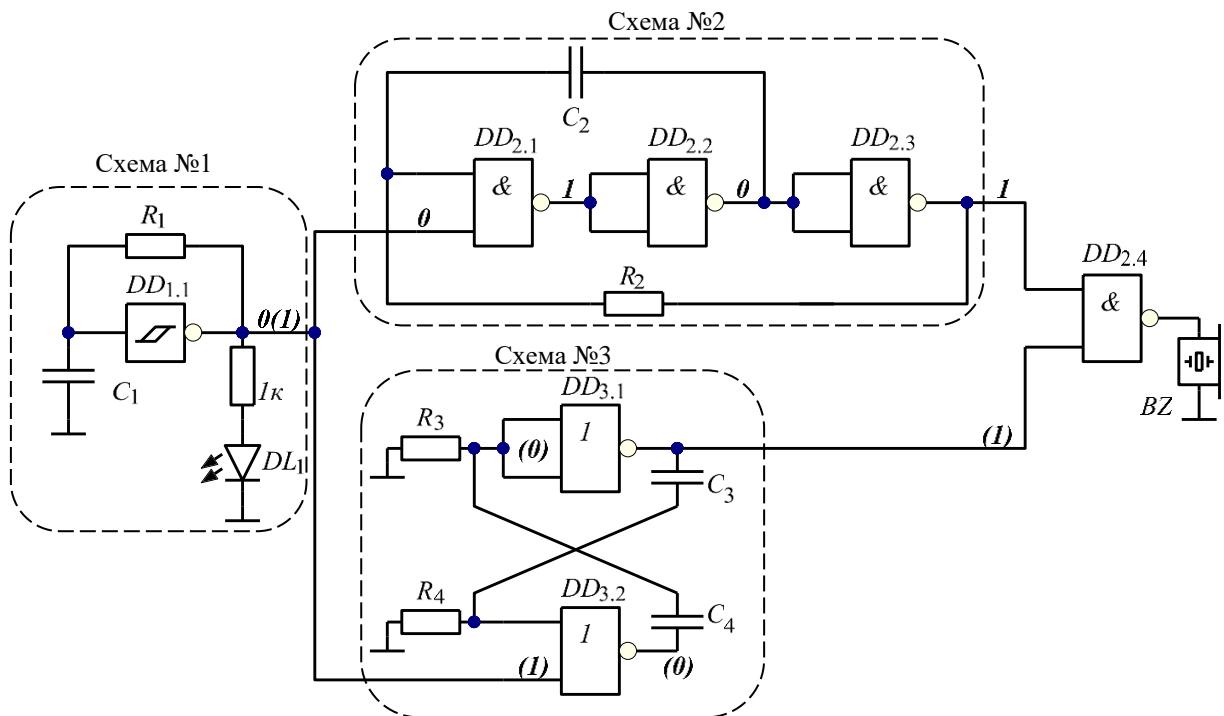

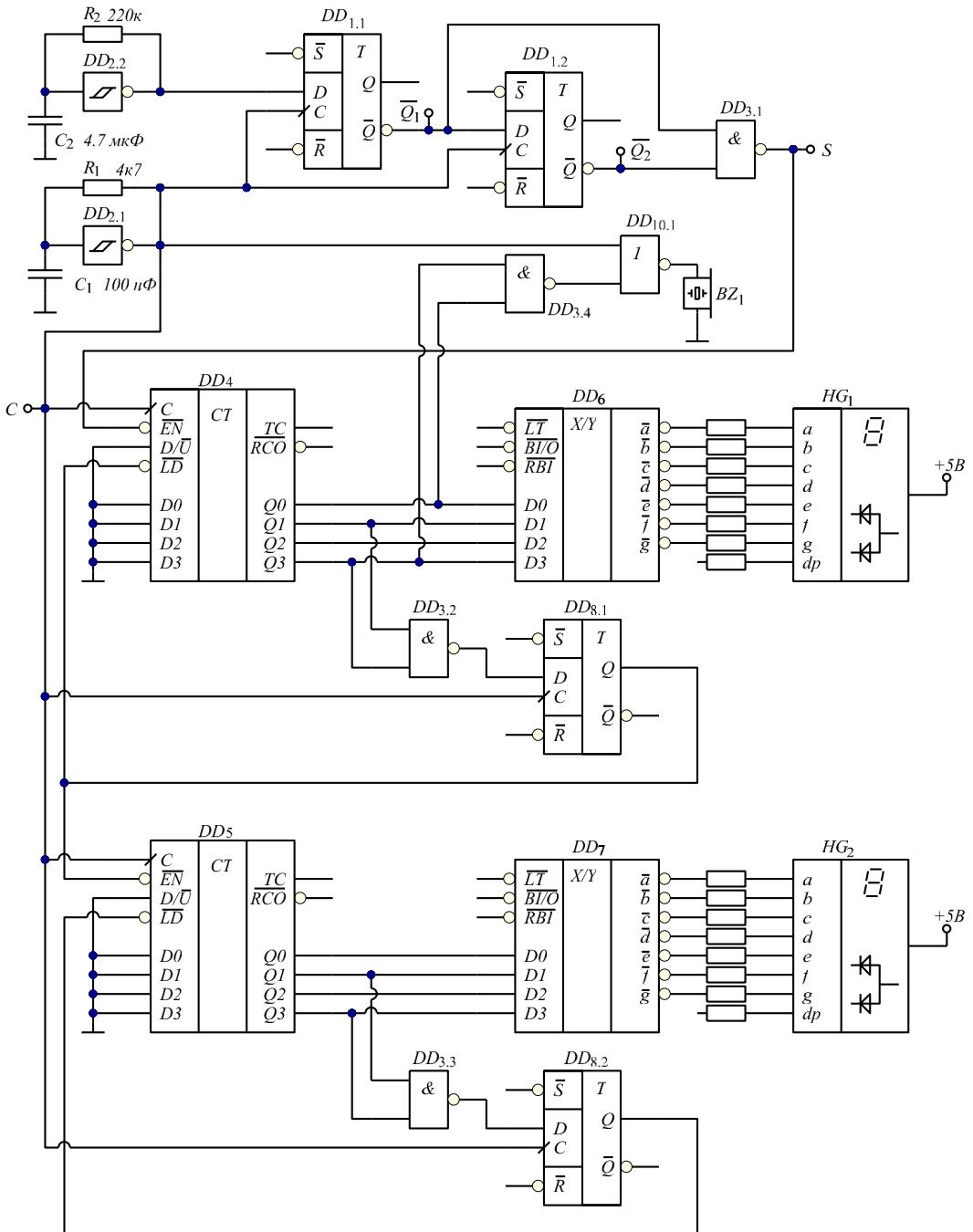

10. Не разбирая собранных схем №№1-3, соберите схему генератора двухтонального звукового сигнала. Параметры времязадающих цепей рассчитаны так, что схемы №№2 и 3 генерируют частоты звукового диапазона, а схема №1 – небольшую частоту (0.1 – 10 Гц).

Двухтональный звуковой сигнал – сигнал, в котором чередуются две различные частоты. Для его создания нужна схема, поочередно подающая на излучатель звука одну из двух звуковых частот (со схем №2 и №3). Выбор частоты происходит под управлением логического уровня, поступающего со схемы №1. Формально такая задача решается при помощи цифрового мультиплексора, однако для упрощения задачи схемы №1 и №3 можно дополнить входами разрешения с различными активными уровнями согласно Рис. 34.

В течение времени импульса  $t_{\text{из}}$  схемы №1 на выходе  $DD_{1.1}$  действует уровень лог. «1». Этот уровень поступает на схему №3, на один из входов ЛЭ  $DD_{3.2}$ , обеспечивая на его выходе постоянный уровень лог. «0» т.к.  $\overline{X + 1} = 0$ . Соответственно, на выходах  $DD_{3.1}$  удерживается лог. «0», а на выходе – постоянный уровень лог. «1».

В то же самое время уровень лог. «1» на входе схемы №2, ЛЭ  $DD_{2.1}$ , не меняет работы этой схемы, т.к.  $\overline{X \cdot 1} = \overline{X}$ , и на ее выходе генерируются прямоугольные импульсы звуковой частоты  $f_2 = \frac{1}{t_{и2} + t_{п2}}$ .

В течение времени паузы схемы №1 ( $t_{п1}$ ) ситуация обратная. Работа схемы №2 заблокирована:  $DD_{2.3}$  удерживает на своем выходе и на выходе всей схемы уровень лог. «1», т.к.  $\overline{X \cdot 0} = 1$ . При этом работа схемы №3 разрешена, т.к. для  $DD_{3.2}$  справедливо выражение  $\overline{X + 0} = \overline{X}$ , и на ее выходе генерируются прямоугольные импульсы с частотой  $f_3 = \frac{1}{t_{и3} + t_{п3}}$ .

Рис. 34. Схема двухтонального звукового сигнала

Иными словами, схемы 2 и 3 работают поочередно. Активная схема выдает прямоугольные импульсы, а отключенная – постоянный уровень лог. «1». Эти два сигнала поступают на вход ЛЭ 2ИЛИ-НЕ,  $DD_{2.4}$ . Лог. «1» на одном из входов не запрещает переключение ЛЭ под управлением сигнала, присутствующего на другом входе:  $Y = \overline{X \cdot 1} = \overline{X}$ , где  $X$  – сигнал, поступающий от активной схемы мультивибратора.

Иными словами, работу всей схемы можно описать выражением:

$$Y = \begin{cases} f_2, & \text{если } U_{\text{вых1}} = 1 \\ f_3, & \text{если } U_{\text{вых1}} = 0 \end{cases}$$

Светодиод  $DL_1$  служит для индикации, какая из двух схем генераторов звуковой частоты активна в данный момент: схема №2, если светодиод светится, и №3 – если отключен. К выходу всей схемы (к выходу  $DD_{2.4}$ ) подключите пьезокерамический зуммер (выдается преподавателем).

11. Подключите канал №1 осциллографа к выходу схемы №1, канал №2 – к выходу ЛЭ  $DD_{2.4}$  и настройте синхронизацию по фронту канала №1.

12. Подберите масштаб по оси времени так, чтобы в кадр входило по нескольку периодов  $T_2 = 1/f_2$  и  $T_3 = 1/f_3$ . Точка синхронизации – в центре экрана по оси времени (используйте кнопку осциллографа «Horizontal / Set to Zero»). Иными словами, на осциллограмме должен быть наглядно виден переход от частоты  $f_3$  к частоте  $f_2$ .

13. Зарисуйте или сфотографируйте полученную осциллограмму.

14. Перенастройте осциллограф на синхронизацию по срезу на канале №1 и повторите пп. 12-13. Пронаблюдайте переход от частоты  $f_2$  к частоте  $f_3$ .

15. К отчету по лабораторной работе приложите полученные осциллограммы.

### 3. ИССЛЕДОВАНИЕ СХЕМ ТРИГГЕРОВ

#### 3.1. Краткое описание лабораторной работы

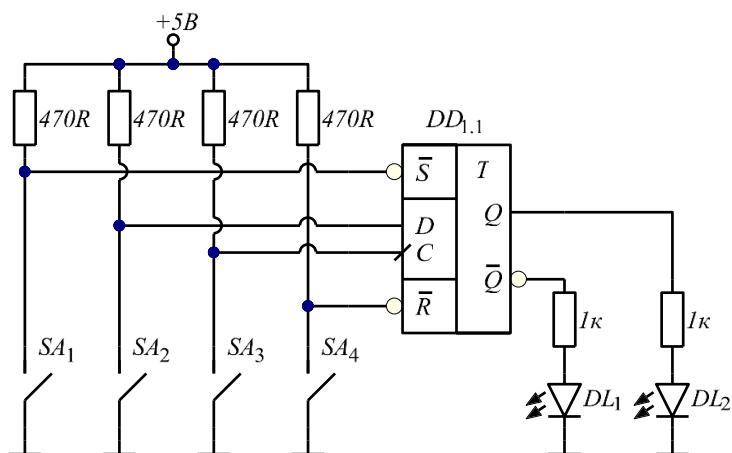

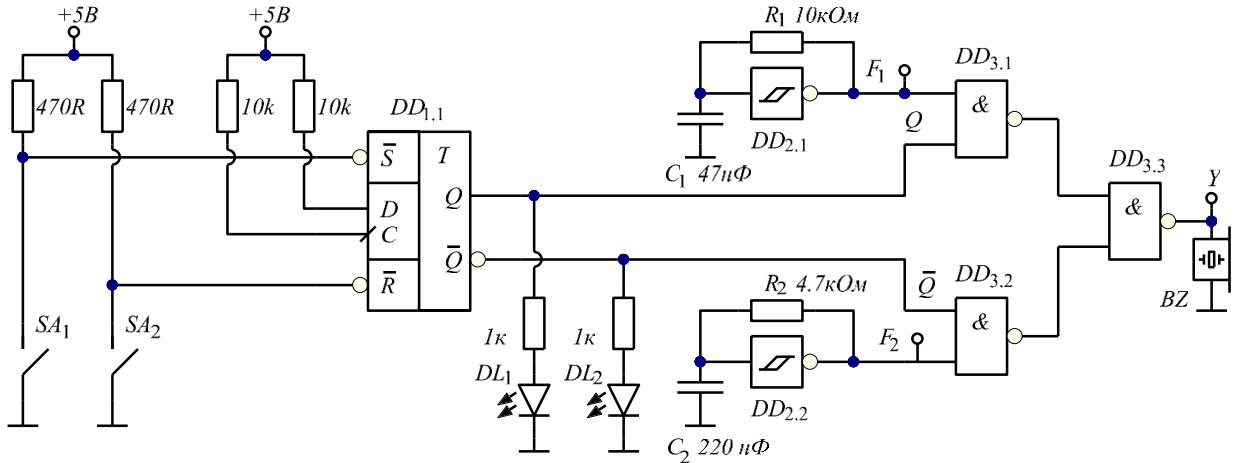

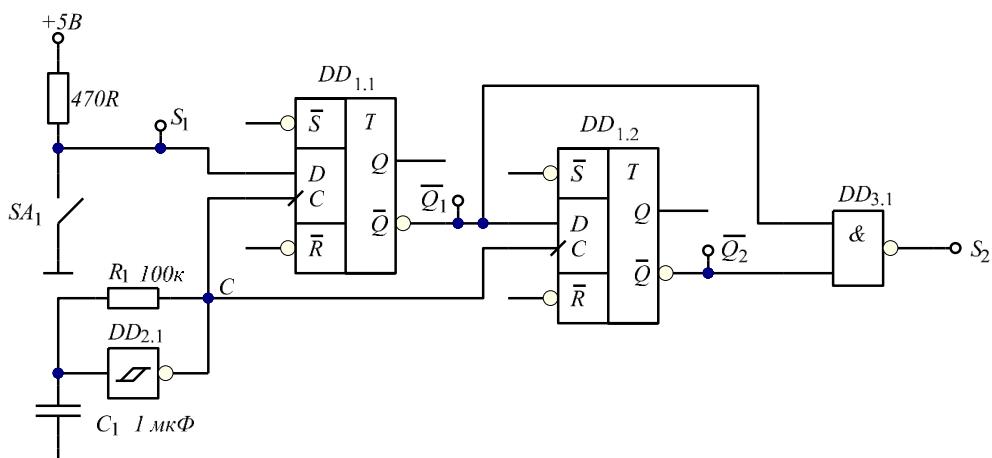

1. В лабораторной работе собираются и исследуются простейшие схемы RS-триггеров на ЛЭ, а также D-триггер с асинхронными входами сброса и установки типа 74HC(HCT)74.

2. Для сборки схем простейших RS-триггеров используются универсальные ЛЭ 2И-НЕ, 2ИЛИ-НЕ.

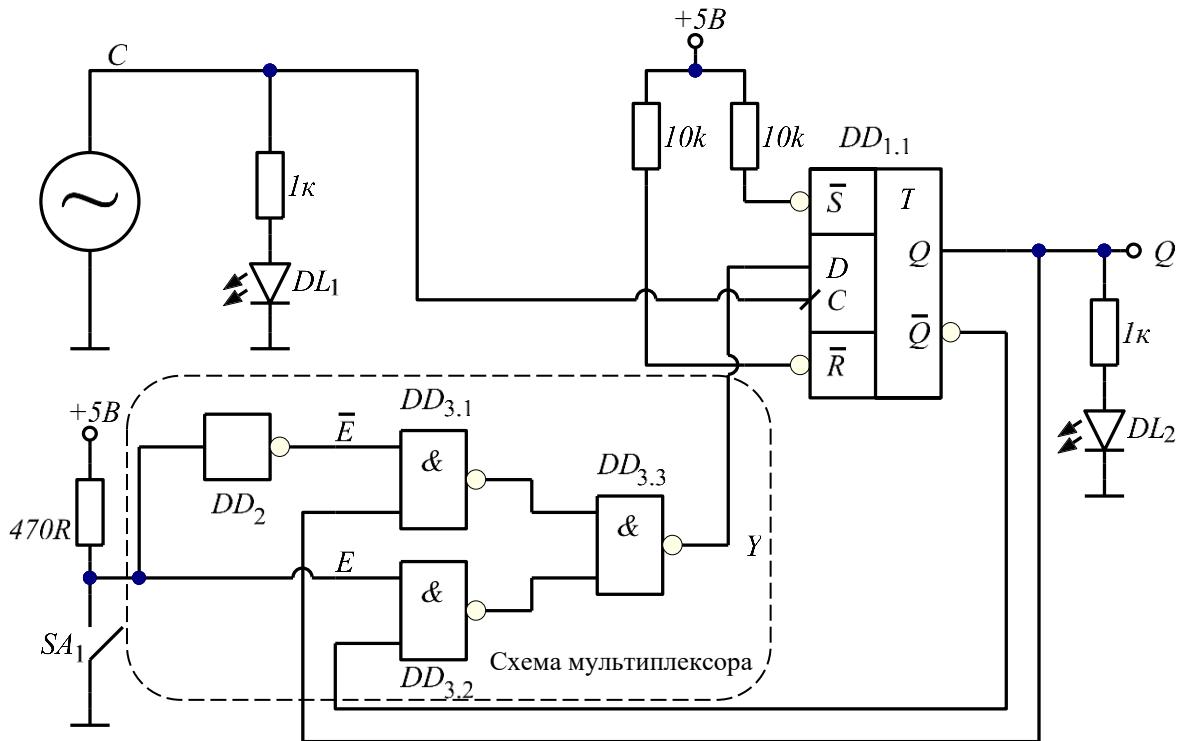

3. На основе D-триггера 74HC(HCT)74 собирается схема пересчетного синхронного Т-триггера с входом разрешения.

4. Входные сигналы для собранных схем поступают с кнопок и генератора, выходные сигналы исследуются осциллографом и индицируются светодиодами.

5. На основе схем простых мультивибраторов и триггера собирается схема генератора звуковой частоты. Выбор частоты осуществляется нажатием кнопок без фиксации.

#### 3.2. Основные теоретические сведения

Триггер – простейшее устройство последовательностной логики. В отличие от комбинаторной логики, где состояния выходов схемы определяются только текущими состояниями входов, в комбинаторной логике уровни выходов зависят еще и от предыдущего состояния системы, имевшего место до последнего изменения уровней входов. Соответственно, последовательностные цифровые схемы имеют способность запоминать свое состояние. Простейшее устройство, способное хранить информацию – триггер: схема на ЛЭ или готовая микросхема, хранящая логический уровень, или один бит данных.

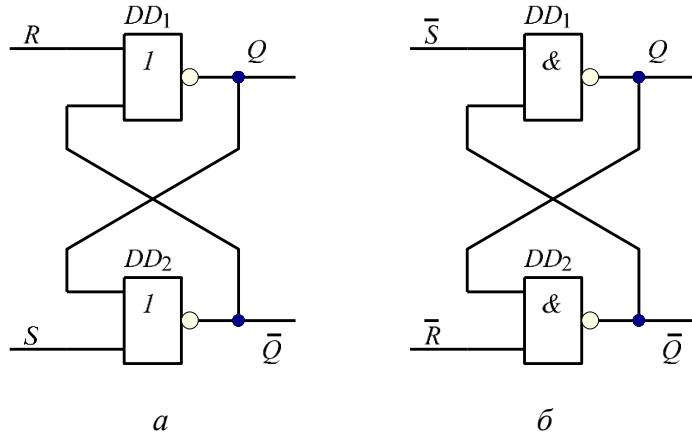

Простейший из триггеров, который можно построить на логических элементах – RS-триггер. Своё название он получил в соответствии с существующими у него входами управления:  $R$  (от англ. «reset», сброс) и  $S$  (от англ. «set», установка).

Схема такого триггера на ЛЭ типа ИЛИ-НЕ показана на Рис. 35, а. Принцип ее действия предельно прост. Предположим, в данный момент на входах схемы  $R$  и  $S$  действует уровень лог. «0», а на выходе схемы  $Q$ , называемым прямым выходом, действует некоторый уровень  $Q^n$ . Согласно принципу действия ЛЭ  $DD_2$ , на его выходе уровень будет равен  $\overline{Q^n + 0} = \overline{Q^n}$ . Выход  $\overline{Q^n}$  называют инверсным выходом триггера. Логический уровень с выхода  $\overline{Q^n}$  поступает на второй вход ЛЭ  $DD_1$ , и на выходе продолжает действовать уровень  $\overline{Q^n + 0} = Q^n$ . Благодаря перекрестному включению ЛЭ, формирующему своего рода положительную обратную связь, пока оба входа  $R$  и  $S$  установлены в лог. «0», состояние схемы не изменится, т.е. триггер находится в режиме хранения бита.

Если на вход  $R$  подать уровень лог. «1» (а на входе  $S$  будет оставаться лог. «0»), то вне зависимости от значения  $\overline{Q^n}$ , согласно принципу действия ЛЭ ИЛИ-НЕ, на выходе  $DD_1$  установится новый уровень  $Q^{n+1} = \overline{Q^n + 1} = 0$ . Этот логический уровень поступает на вход  $DD_2$ , и на его выходе формируется уровень  $\overline{Q^{n+1}} = \overline{0 + 0} = 1$ . Иными словами, подача уровня лог. «1» на вход  $R$  привела к сбросу триггера (к записи в него нулевого значения). Т.к. лог. «0» не меняет состояние схемы, а лог. «1» устанавливает  $Q = 0$ , вход  $R$  называется *входом сброса с активным высоким уровнем*.

Рассуждая совершенно аналогично, несложно убедиться в том, что подача лог. «1» на вход  $S$  при  $R = 0$  и при любом  $Q^n$  устанавливает  $Q^{n+1}=1$ , т.е. вход  $S$  является *входом установки с активным высоким уровнем*. В принципе, это следует и из описанного выше принципа действия входа  $R$  с учетом полной симметрии схемы.

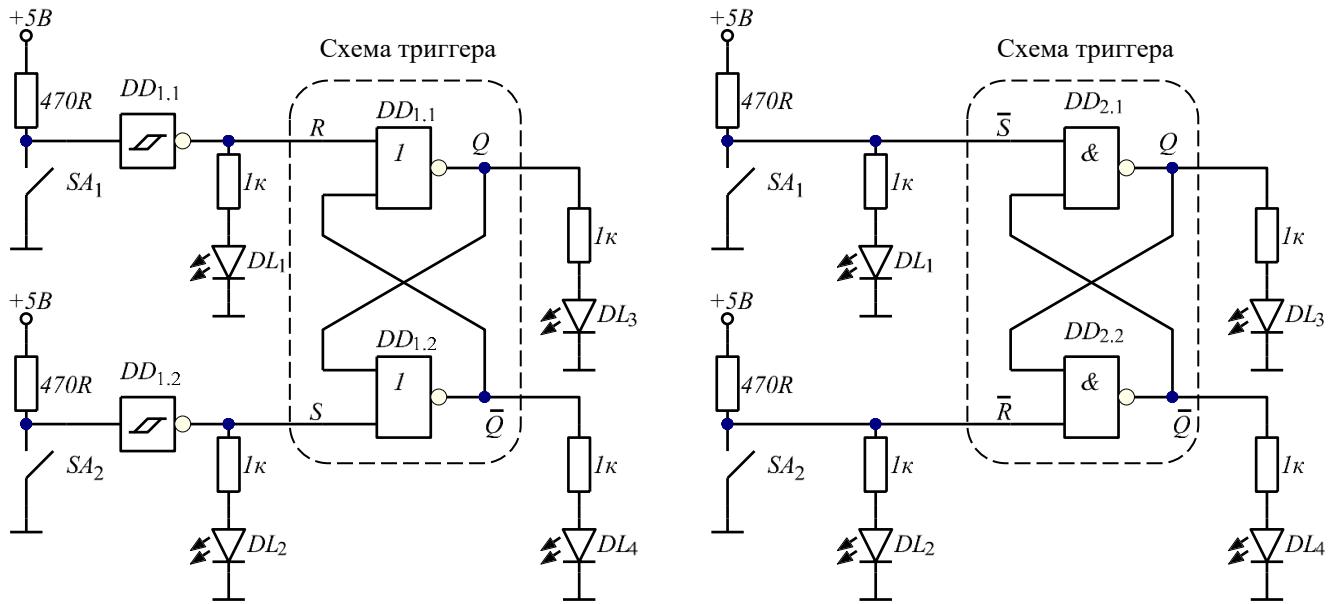

Рис. 35. Схемы RS-триггера на ЛЭ ИЛИ-НЕ (а), И-НЕ (б)

При одновременной подаче уровня лог. «1» на оба входа, на обоих выходах схемы устанавливаются уровни лог. «0». Какой логический уровень будет действовать на выходе  $Q$  после снятия активных уровней с входов, определится лишь тем, с какого входа уровень будет снят последним (в реальности одновременно изменить логические уровни в двух разных цепях невозможно). Для схемы RS-триггера комбинация двух активных уровней на входах установки и сброса считается запрещенной, т.к. схема перестает выполнять свою основную функцию.

Немного отличается от рассмотренной схемы вариант RS-триггера на элементах И-НЕ (см. Рис. 35, б). Нетрудно убедиться в том, что если установить  $\bar{R} = \bar{S} = 1$ , состояние схемы не изменяется. Установка  $\bar{R} = 1, \bar{S} = 0$  переводит выход  $Q$  в состояние лог «1», а  $\bar{R} = 0, \bar{S} = 1$  – в лог. «0». То есть, выходы сброса и установки у такого RS-триггера имеют низкий активный уровень, а запрещенной комбинацией является, соответственно,  $\bar{R} = \bar{S} = 0$ . Обратите внимание, что взаимное расположение входов сброса/установки и прямого/инверсного выходов у двух крайне похожих друг на друга схем – разное.

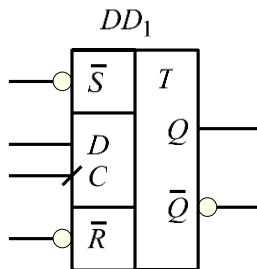

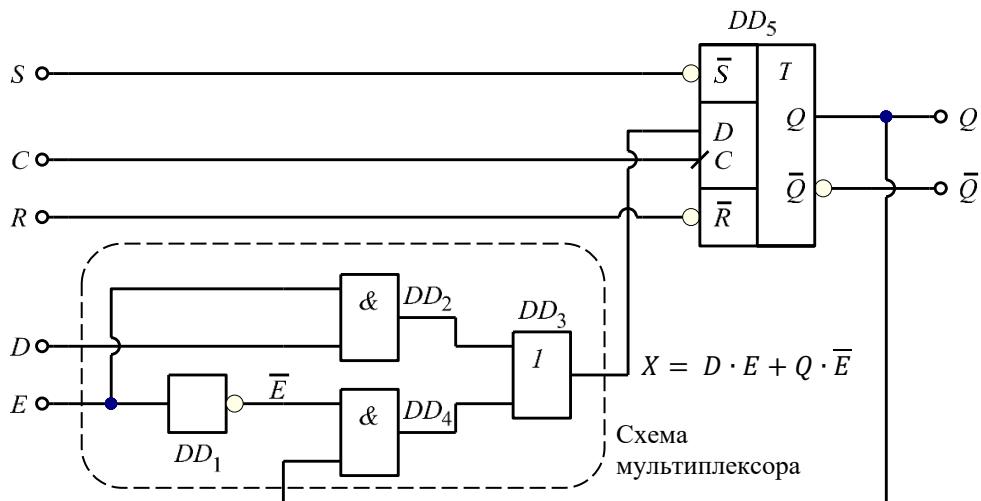

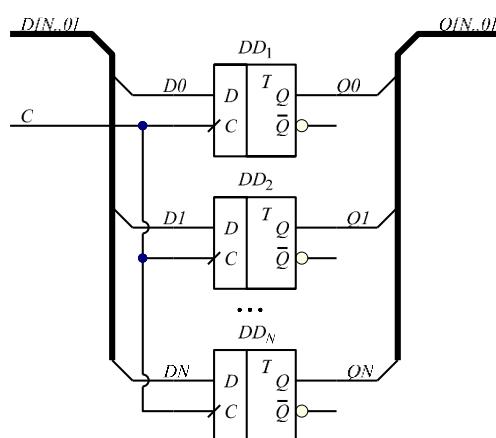

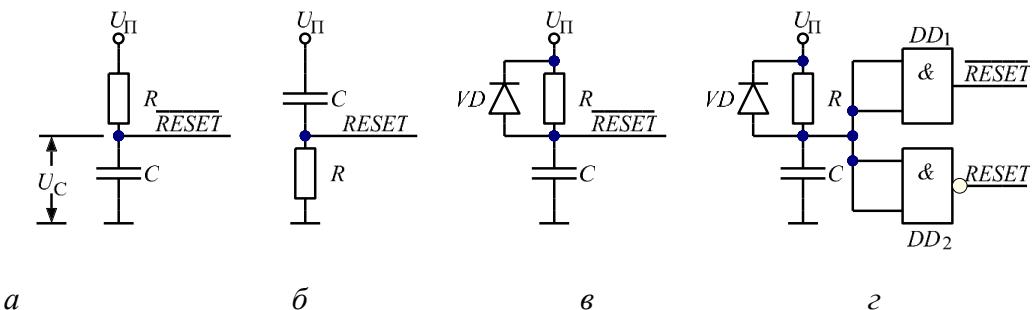

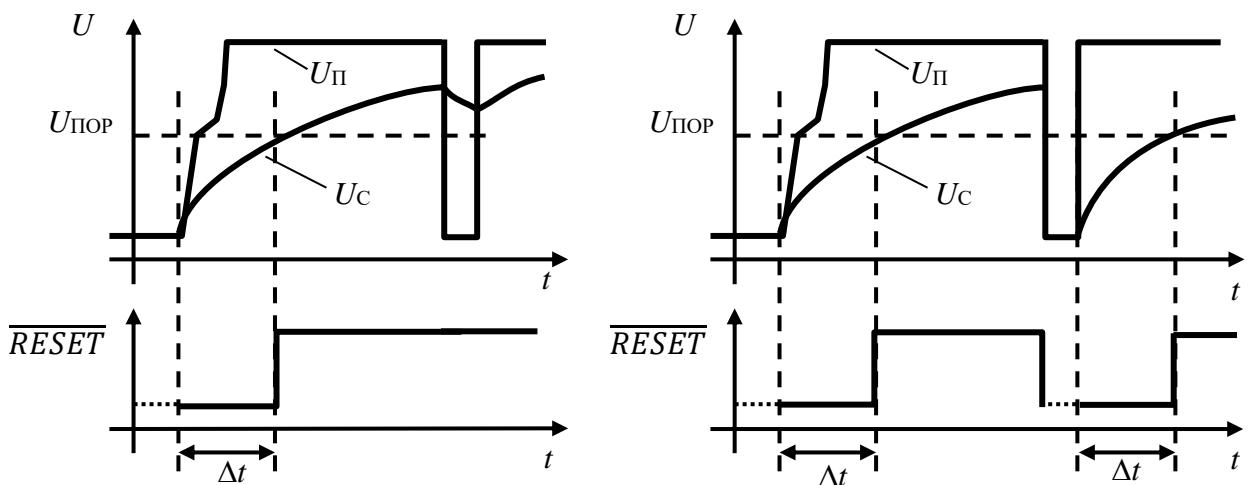

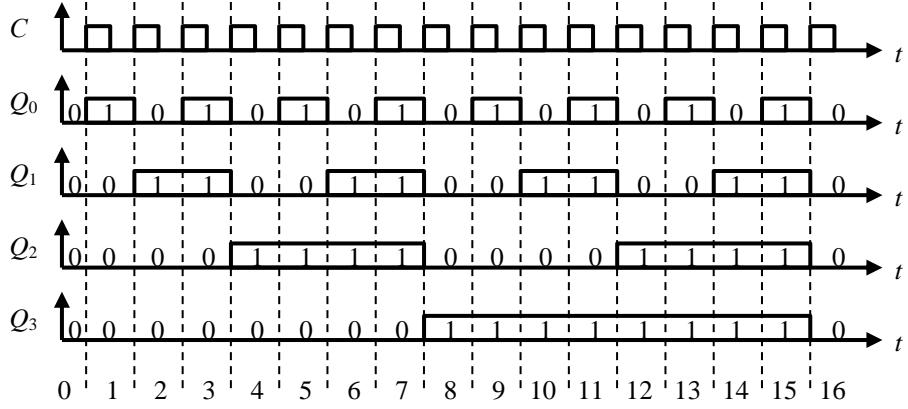

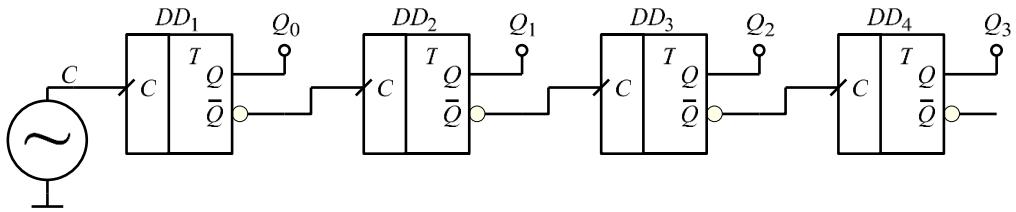

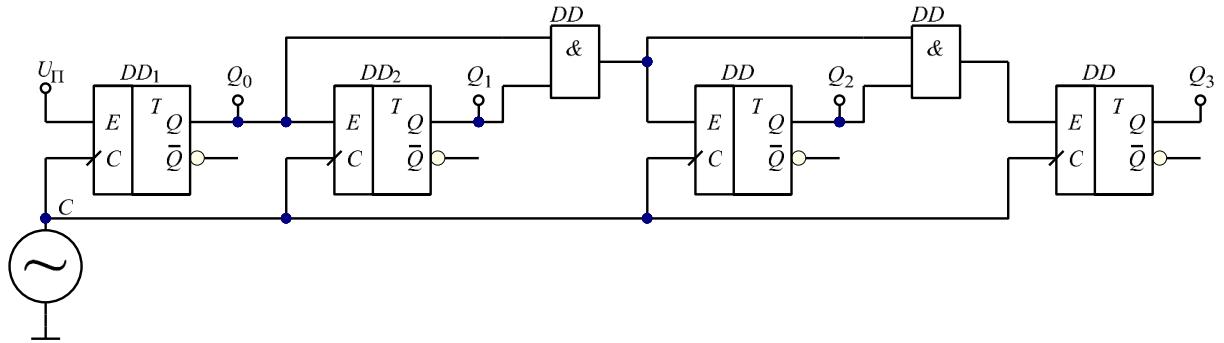

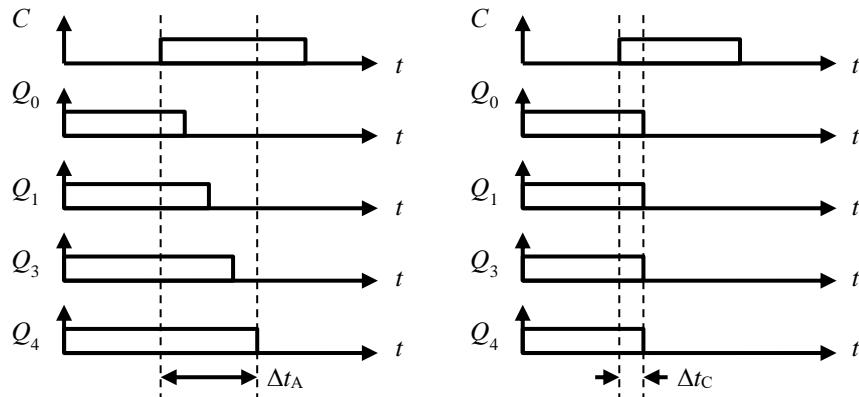

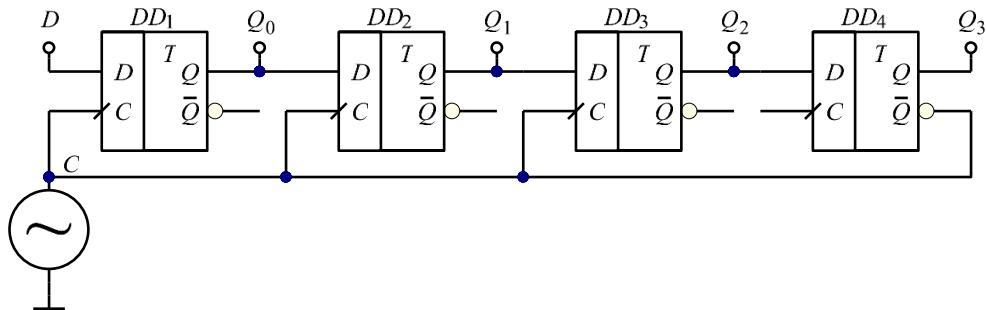

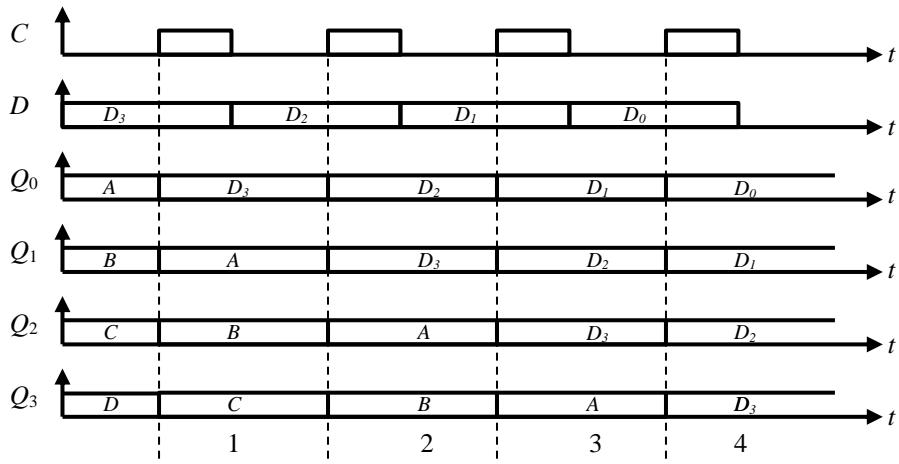

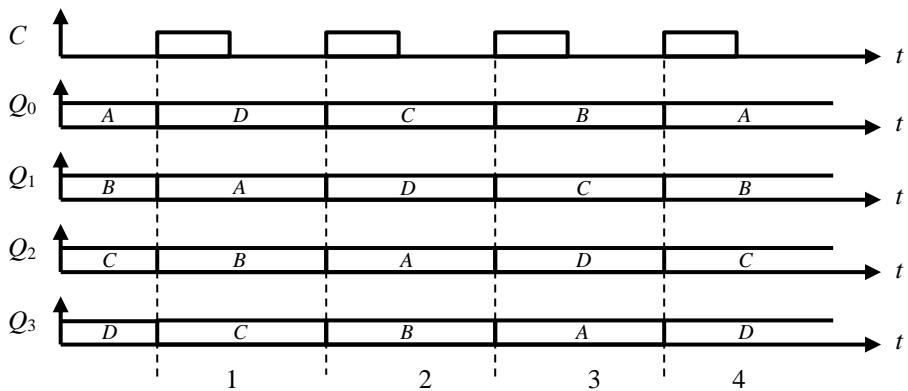

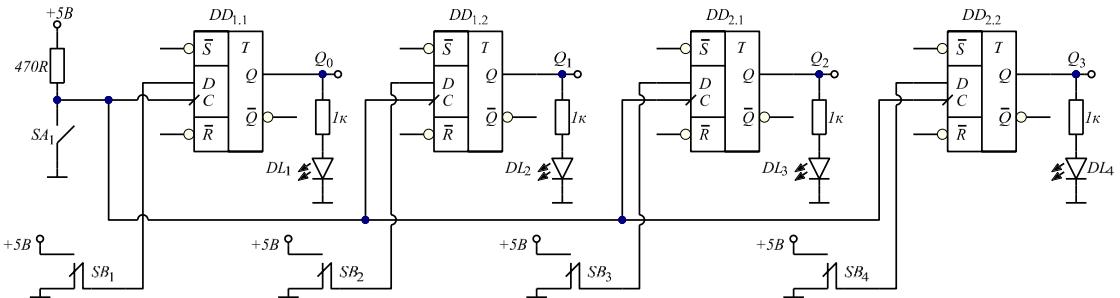

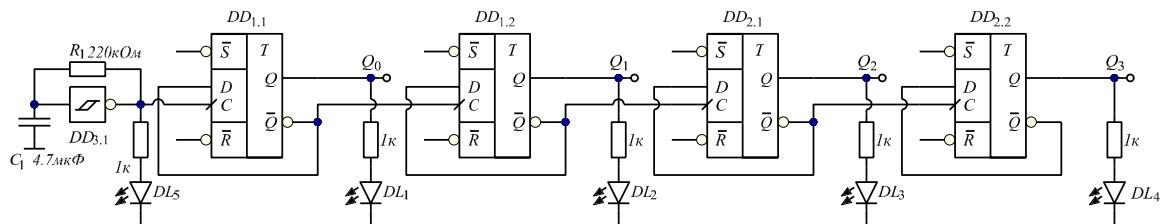

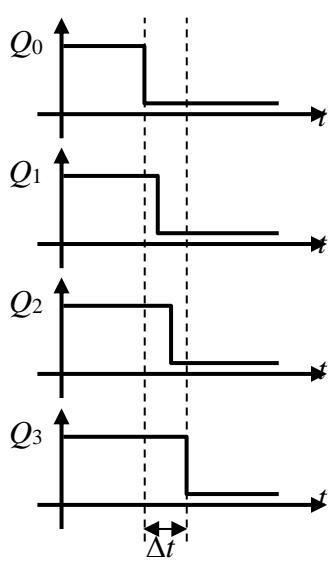

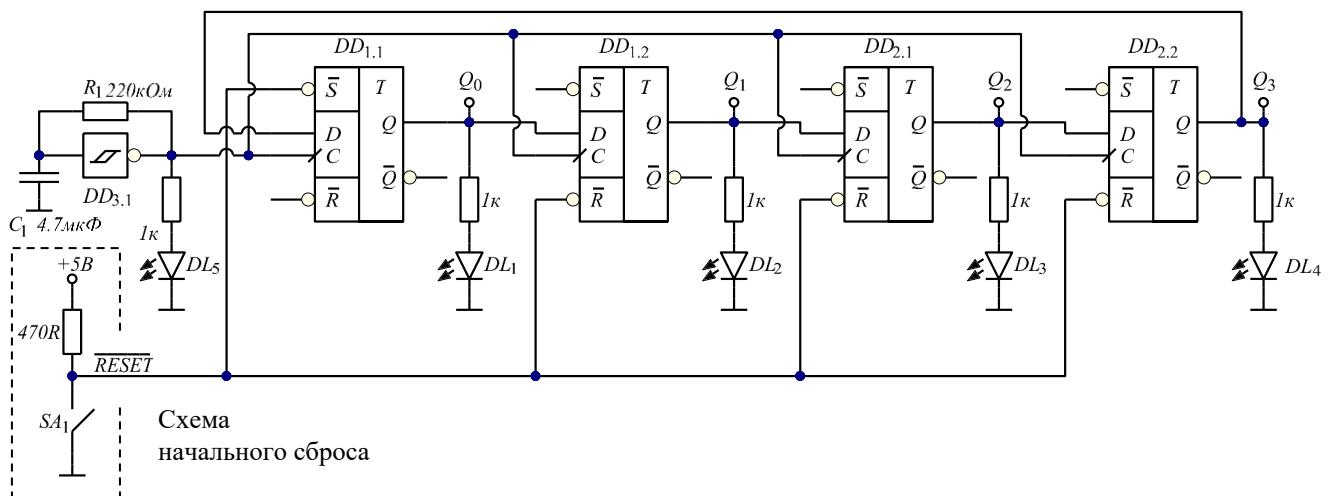

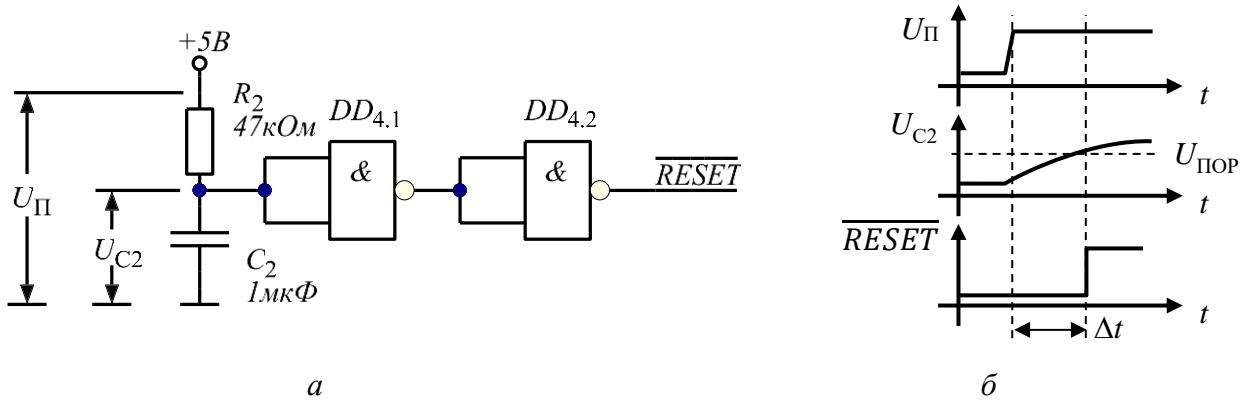

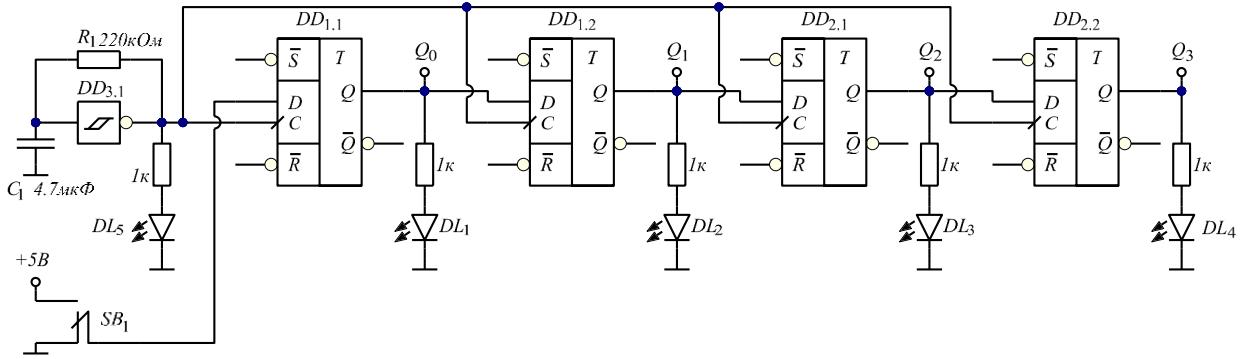

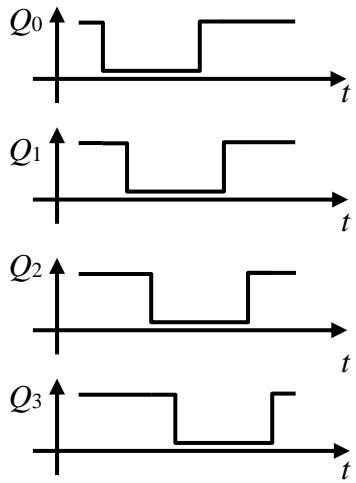

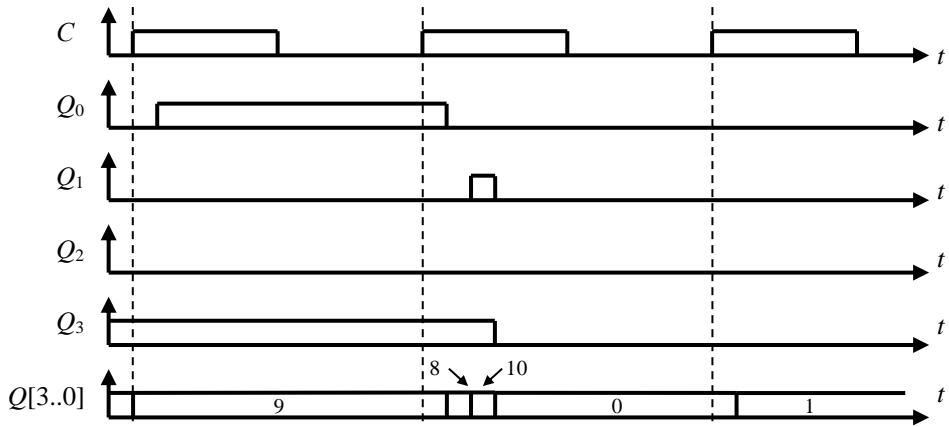

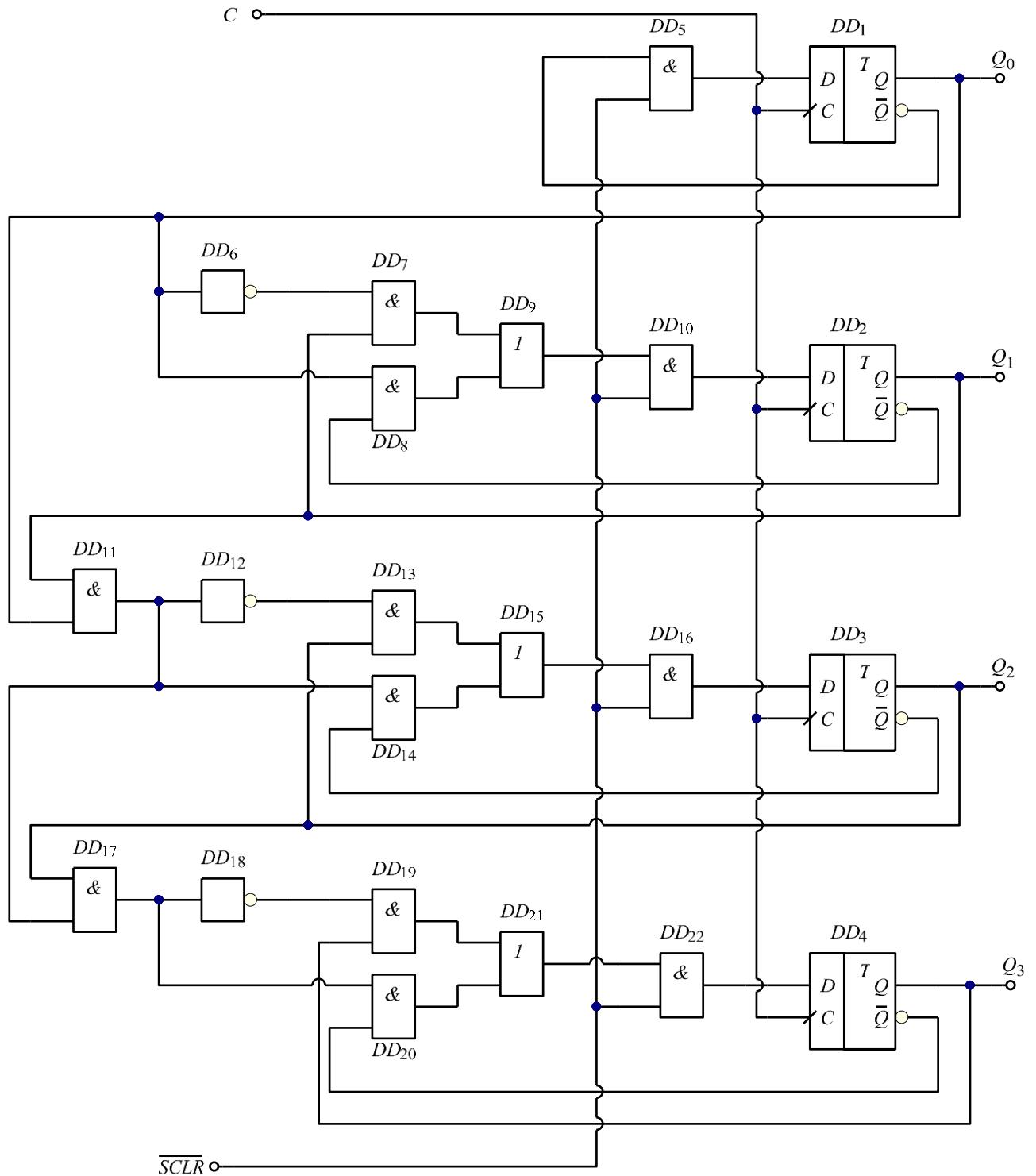

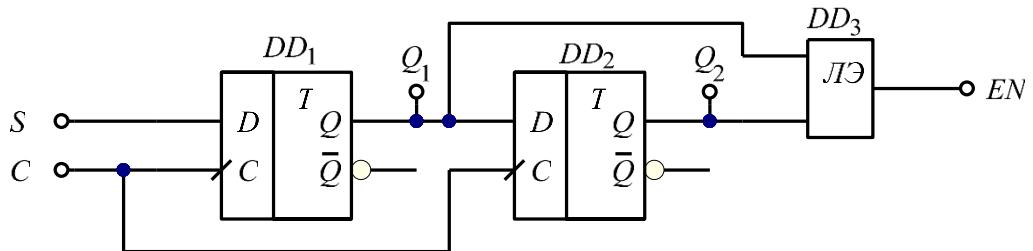

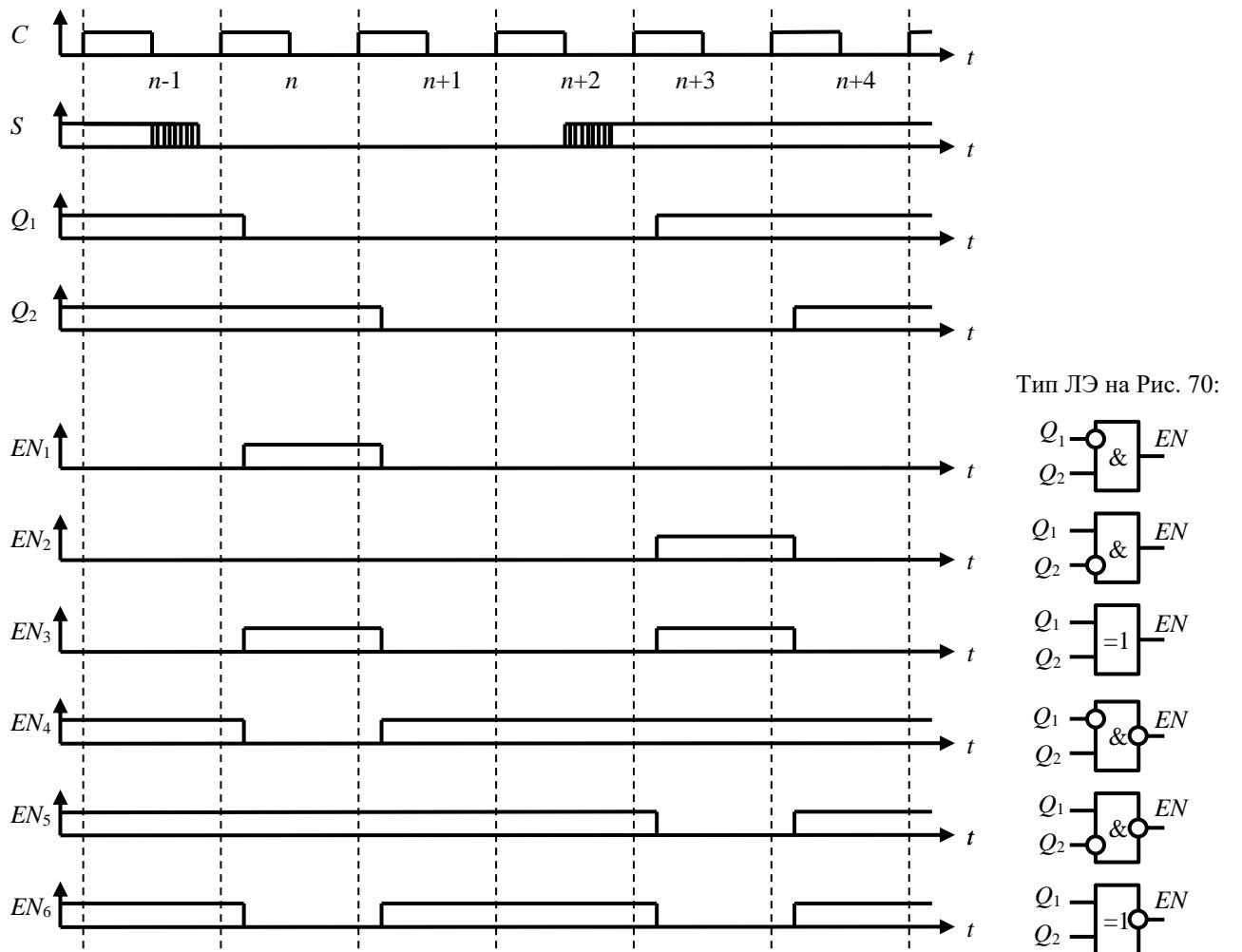

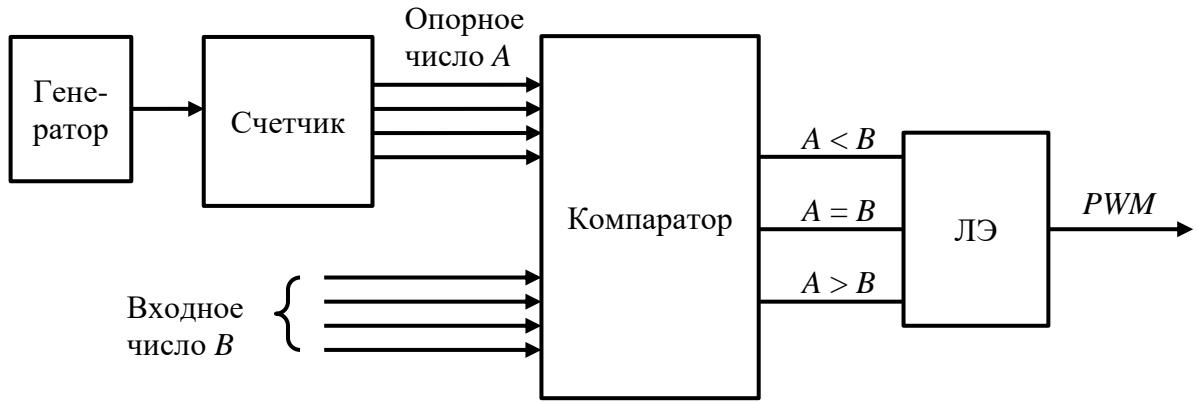

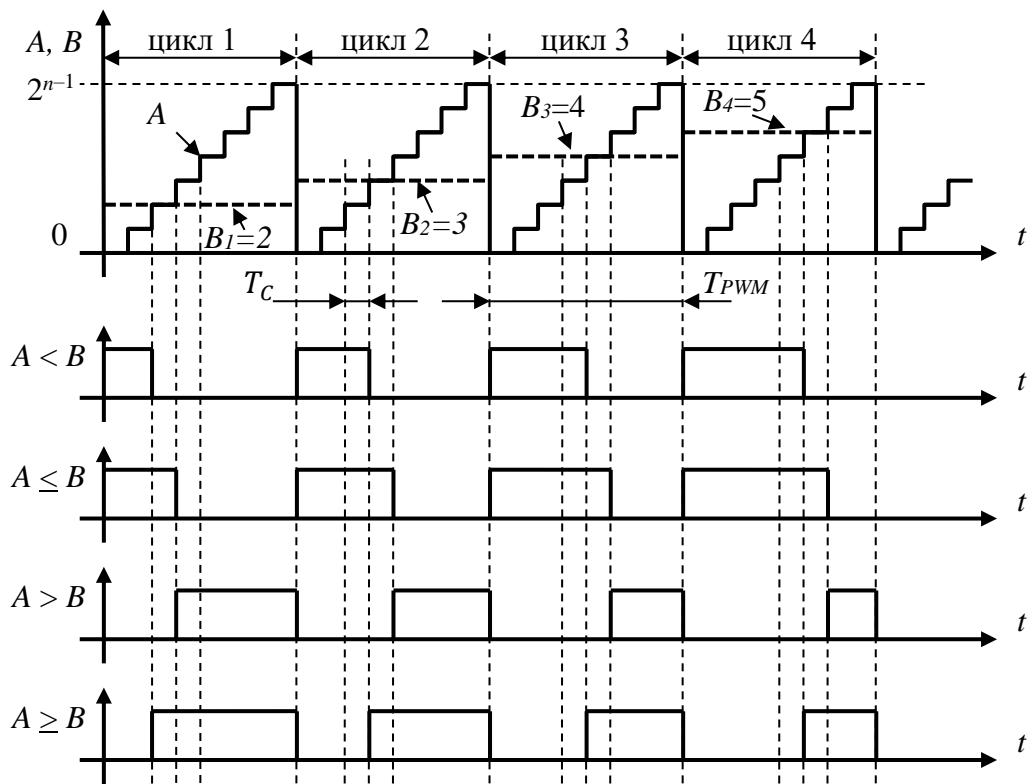

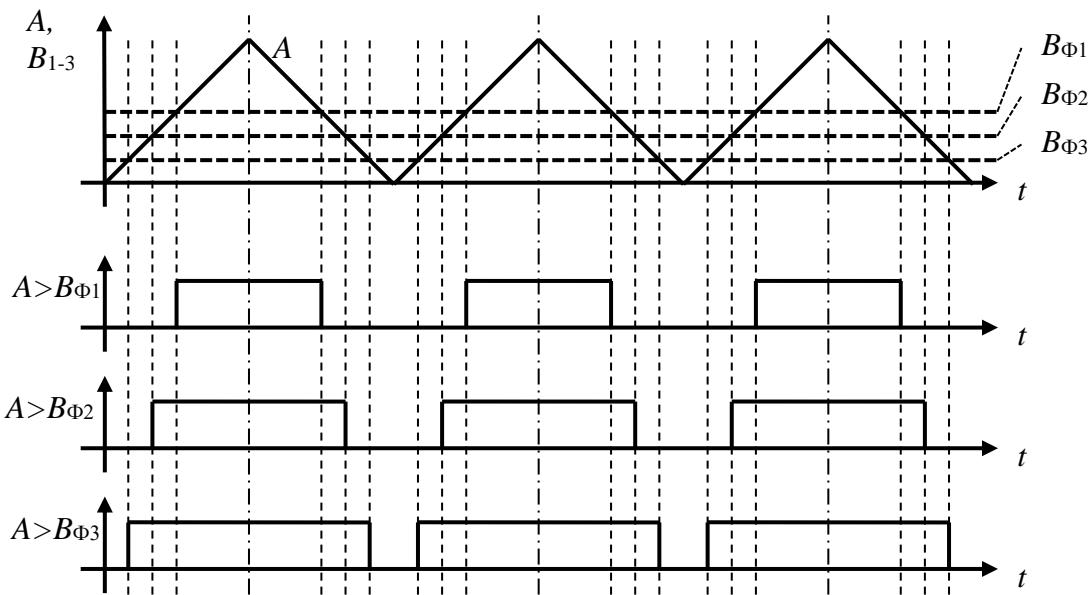

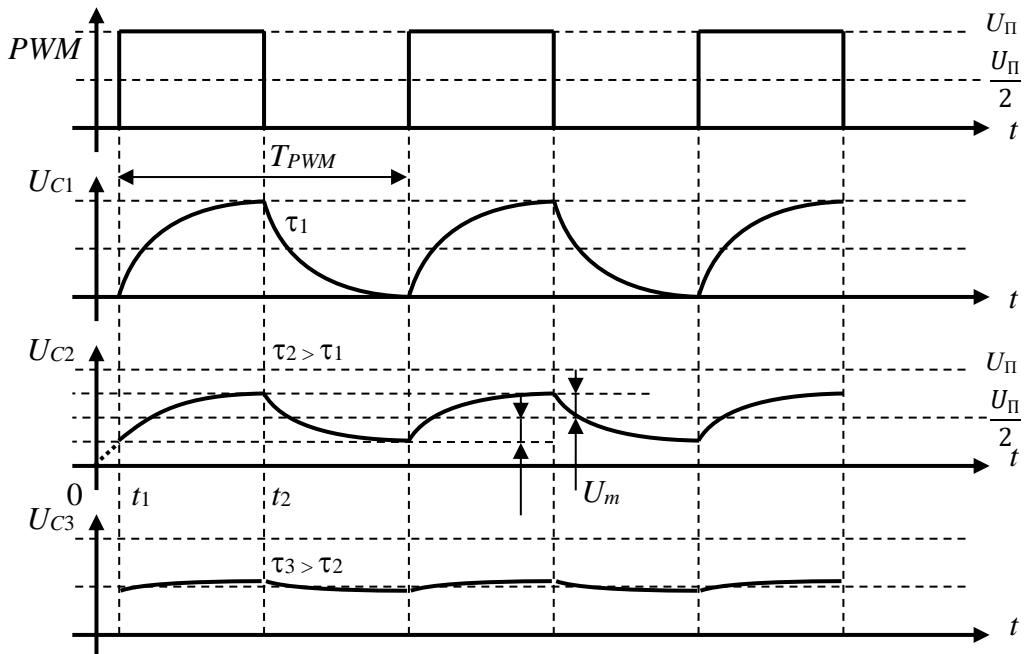

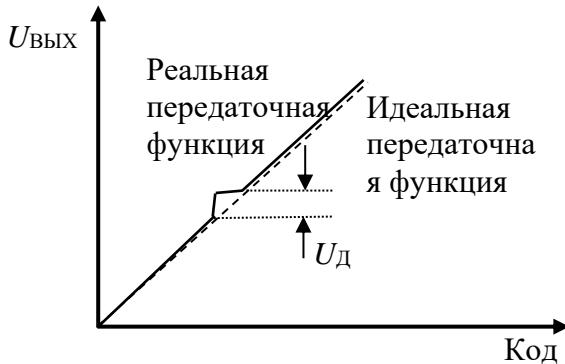

Помимо RS-триггера существует еще множество схем триггеров со своими входами управления и особенностями работы. Описание схемотехнических реализаций всех триггеров на ЛЭ не входит в задачи настоящих методических указаний и широко описаны в литературе. Отметим лишь, что существуют, в частности: